# 逢甲大學學生報告 ePaper

## 報告題名:

高電子遷移率電晶體高頻參數萃取與微波模型建立

作者:何秋聖、呂典陽、林正哲

系級:電子系

學號: d9150121

開課老師:李景松 老師

課程名稱:化合物半導體元件

開課系所:資電學院電子元件四

開課學年: 九十四 學年度 第一學期

## 中文摘要

在微波通信與個人行動通信無線網路系統蓬勃發展潮流 激勵下,微波積體電路技術與高性能多功能高速元件,已廣 泛地成為學術研發與產業需求之研究焦點。尤其單晶微波積 體電路(MMIC)設計方面,高電子遷移率電晶體(HEMT)應用 範圍大幅成長,逐漸成為射頻積體電路(RFIC)元件之關鍵技 術。

在這篇報告中,我們將要報告高電子遷移率電晶體 (HEMT)發展歷程與結構特性,應用在小訊號等效電路模型的建立上。HEMT 最大的優點就是擁有高電荷密度的二維電子雲及高速度的載子遷移率。由於 HEMT 擁有高電子遷移率,使得該元件的轉導值非常高,且也可改善元件的高頻特性,所以 HEMT 應用在行動電話及衛星通訊技術及軍事方面有很大的幫助。

無線通訊技術產品是由許多被動電路所組成的高速半導體元件。應用在無線通訊最主要的就是改善高頻特性,因此萃取高頻參數,對於射頻積體電路模型的建立是很重要的關鍵。

我們知道小訊號等效電路對於場效電晶體的特性分析,如:增益、雜訊…等,是非常有幫助的,在設計微波電路及元件的製程。我們將量測到的小訊號等效電路中元件的數值,帶入軟體並且建立元件模型,接著調變數值使得我們所模擬出的參數值與實際值接近,就可以成功萃取出真實的元件數值。得到我們想要的結果並完成該報告。

關鍵字:HEMT、高頻、參數萃取、小訊號等效電路

#### **Abstract**

With wireless communication systems moving toward larger user capacity and higher data rate and the demand for high-frequency, thus the high-performance devices are increasing on a global scale. The high-speed microwave device manufacturers for global trade are important. This category includes Metal-Semiconductor Field-Effect Transistor (MESFET), High Electron Mobility Transistor (HEMT), and Heterojunction Bipolar transistor (HBT), etc...

In this term paper, we will report the HEMT historical evolution, structures, applications and high-frequency model build-up. The material properties that have the greatest impact on the high-speed performance of HEMTS are the high sheet charge density in the two-dimensional electron gas (2DEG) and the superior electron velocity. Since HEMT has high-speed electron mobility, it can result in higher transconductance (g<sub>m</sub>) and improved high-frequency characteristics. So the demands for the HEMT applied to the cell-phone, satellite communication and military have been growing tremendously.

Various kinds of wireless communication technological products are formed by lots of various passive circuits, composed of high-speed semiconductor devices. The device high-frequency characteristics are essential in improving quality of the wireless communication products. Therefore, the extraction of the high-frequency parameters is the key point for the RF model build-up.

Knowledge of the small-signal equivalent circuit of a field-effect transistor is very useful for the device performance analysis (gain, noise, etc.) in designing microwave circuits and characterizing the device processing. Usually, the small-signal equivalent circuit is obtained by optimizing the component values to closely fit the device measurement results of the small-signal microwave scattering parameters. Consequently, this is the main motive for working on this term project.

## 【目錄】

| 第一章 元件簡介                | 1  |

|-------------------------|----|

| 1-1 研究動機與研究問題           | 1  |

| 1-2 元件簡介                | 4  |

|                         |    |

| 第二章 高點子遷移率電晶體工作原理       | 17 |

| 2-1 工作原理                | 17 |

| 2-2 二維電子氣               | 31 |

|                         |    |

| 第三章 元件製程特性量測            | 38 |

| 3-1 元件的基本結構             | 41 |

| 3-1-1 覆蓋層               | 41 |

| 3-1-2 蕭基層               | 42 |

| 3-1-3 δ 摻雜載子提供層         | 42 |

| 3-1-4 隔離層               | 43 |

| 3-1-5 假晶性 InGaAs 通道層    | 44 |

| 3-1-6 緩衝層               | 44 |

| 3-2 磊晶成長技術              | 46 |

| 3-2-1 金屬有機化學氣相沉積(MOCVD) | 46 |

| 3-2-2 分子束磊晶(MBE) | 51 |

|------------------|----|

| 3-3 元件的製程        | 55 |

| 3-3-1 樣本定位       | 55 |

| 3-3-2 源極和洩極金屬化   | 56 |

| 3-3-3 高台絕緣       | 58 |

| 3-3-4 閘極蕭基接觸     | 59 |

| 3-4 元件的特性與量測     | 60 |

| 3-4-1 霍爾量測       | 60 |

| 3-4-2 量測之樣本介紹    | 65 |

| 3-4-3 元件的 I-V 量測 | 67 |

|                  |    |

| 第四章 元件高頻參數萃取     | 73 |

| 4-1 晶圓量測         | 74 |

| 4-2 參數量測與模型建立    | 76 |

| 4-2-1 S 參數量測法    | 77 |

| 4-2-2 模型參數萃取     | 80 |

| 4-2-3 元件模擬與結果分析  | 90 |

|                  |    |

| 第五章 結論           | 99 |

# 第一章 元件簡介

## 1-1 研究動機與研究問題

過去全球半導體的發展重心都是以矽(Si)為材料基礎,但由於矽元素先天上的物理限制,包括電子移動率低、頻率操作範圍小、無法耐高溫操作、高頻操作有大雜訊且不易解決、元件輸出工率與效能低、抗輻射性差、等因素,使其在極高頻應用上受到相當大的阻礙。然而近兩三年來,無線高頻通訊的產品發展迅速,使得III-V族化合物半導體得以脫穎而出。近幾年來III-V族化合物半導體由於有較高的電子移動率,所以已經廣泛地應用在高頻率、高效能、高增益、低雜訊的電晶體上。而III-V的電晶體大致可以分為兩大類:第一類為異質接面双載子電晶體(HBT),另一類為(異質結構)場效電晶體(FET)。而 FET 又可分為下列幾種:

- (1)金屬-半導體場效電晶體(MESFET)

- (2)高電子移動率電晶體(HEMT)

- (3)參雜式通道場效電晶體(DCFET)

- (4)金屬-氧化物-半導體場效電晶體(MOSFET)

在微波通信與個人行動通信無線網路系統蓬勃發展潮流 激勵下,微波積體電路技術與高性能多功能高速元件,已廣 泛地成為學術研發與產業需求之研究焦點。尤其單晶微波積 體電路(MMIC)設計方面,高電子遷移率電晶體(HEMT)應用 範圍大幅成長,逐漸成為射頻積體電路(RFIC)元件之關鍵技 術。

其中 HEMT 由於具有較高的電子移動率,所以可以得較高的轉導值(Transconductor,gm)、較高的高頻特性、較低的雜訊指數,因此 HEMT 已經被廣泛的應用在手機、衛星通訊及軍事用途上。

HEMT 結構中,將載子提供層與未摻雜電子通道 (undoped channel layer)分離,大大改善雜質離子化散射 (ionized-impurity scatteeing)情形,且在未摻雜通道裡,電子達到飽和速度,以及因能隙差異,在未摻雜通道內形成三角量子井的二維電子氣(2DEG),皆使電晶體獲得高電子移動速度。

由於各種無線通訊技術產品皆由各種主被動半導體元件 及電路所構成。其中高頻半導體元件特性好壞與否,對於無 線通訊產品的品質更扮演著舉足輕重的關鍵。為了提供高頻 元件的製程及元件設計者更快速且詳實的元件特性,以作為 進一步改良之依據;並且同時精準地提供電路設計者所需的 資訊,高頻元件測試乃為一非常重要之關鍵技術;因此建立 高頻元件模型之大方向為最佳化等效電路中的元件值,使模 擬與實驗結果之 S 參數(scattering parameter)非常接近,然而 此步驟具有以下障礙:

- (1)需要準確量測的寬頻 S 參數裝置。

- (2)電路中的最佳元件值會隨著最佳化的方法與初始值而有 所改變。

- (3)使其具物理涵義,等效電路需要某些參數的預測值,例 如: 闡極電阻。

為了克服這些困難,我們選擇晶圓高頻探測系統 (wafer-probing system)的方法,可快速且精確量測等效電路中本質與外質的元件值,以得到與電晶體製程相關參數。

## 1-2 元件簡介

### 矽(Si)與砷化鎵(GaAs)比較

矽由於成長成本低,成為半導體元件的主要材料但由於在高頻時,以矽為基體的元件因為漏電流較大而使系的元件在高頻時雜訊也相對變大,致使矽在高頻的應用有限。而砷化鎵(GaAs)由於有高的電子移動率並且以砷化鎵(GaAs)作為基體具有半絕緣特性,故以砷化鎵(GaAs)作成的半導體元件在高頻都具有極佳的頻率響應和低雜訊效應。砷化鎵與矽元件特性比較,砷化鎵的優點如下:

### (1)高電子傳輸速度

可操作頻率達 2~300GHz,,一般通訊頻率在 1GHz 以上時,主要用砷化鎵。

### (2)耐高溫

操作溫度達攝氏 200 度,可靠度較不受熱影響。

#### (3)高抗輻特性

不易產生訊號失真與錯誤的情形,與矽比起來不易受輻射的影響。

## (4)半絕緣特性

砷化鎵的能隙為 1.42eV 大於矽的 1.12eV,因此較 具半絕緣特性可將元件間的訊號損失減低到最小。

砷化鎵元件具微波元件要求的特性:「可操作頻率高、高 頻下使用雜訊小、功率耗損少、元件績效(線性、效率、功 率密度)高、元件面積小...等特性」;高抗輻特性使砷化鎵 元件適用於衛星通訊時暴露於太空中所產生的輻射問題。

又尺寸也是影響主動元件能否操作在微波的重要因素, 元件尺寸越小越能操作在微波頻段,BJT 是以射頻寬度來決 定操作頻段,射極寬度越小在高頻效應越佳。FET 是以閘極 長度來決定操作頻段,閘極長度越小越能操作在高頻,而通 常砷化鎵(GaAs)製程是以電子東來製作閘極長度所以能做到 非常小。故一般砷化鎵(GaAs)較常被應用在微波電路。

|                        | 砷化鎵(GaAs)     | 矽(Si)            |

|------------------------|---------------|------------------|

| 最大頻率範圍                 | 2-300GHz,極具遠程 | 1GHz 以下          |

|                        | 通訊需求          |                  |

| 電子遷移率                  | 8500          | 1500             |

| (cm <sup>2</sup> /V-s) |               |                  |

| 最大操作溫度                 | 攝氏 200 度      | 攝氏 120 度         |

| 電子遷移率                  | 亩             | 低                |

| 抗輻射性                   | 盲             | 低                |

| 具光能                    | 是             | 否                |

| 高頻下使用                  | 雜訊少           | 雜訊多,不易克服         |

| 功率耗損                   | 小             | 古同               |

| 元件大小                   | 小             | 大                |

| 元件績效(線性、               | 高             | 低                |

| 效率、功率密度)               |               |                  |

| 元件整合性                  | 低             | 古问               |

| 主流 wafer 尺寸            | 4吋,進軍6吋,但     | 8 吋,但至 2001 年間將有 |

|                        | 困難度高          | 許多 12 吋廠量產       |

表 1-1 GaAs 與 Si 比較表

但砷化鎵(GaAs)基板都屬於稀有元素製程,成本較高,加上尺寸縮小不易、大尺寸的晶圓生產困難也有高成本的缺點。加上矽製程解決方案在技術方面成熟與革新等因素影響,使得砷化鎵(GaAs)等化合物半導體製程技術在高頻市場的地位逐漸受到矽製程的挑戰。HBT與PHEMT大部分是使用砷化鎵(GaAs)當材料且使用異直接面技術來加快電子移動率,使其在微波應用上有更好的特性。

#### 微波元件的主流-砷化鎵

傳統軍事通訊是以砷化鎵(GaAs)為主要的製程,因發展 多年已是成熟穩定的製程技術。由最初的 GaAs MESFET 演 變成現今的 HEMT 和 HBT 等許多高速元件的發展。

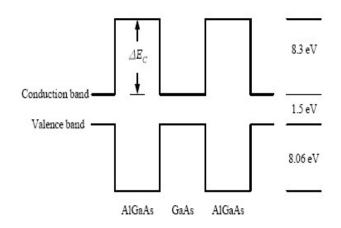

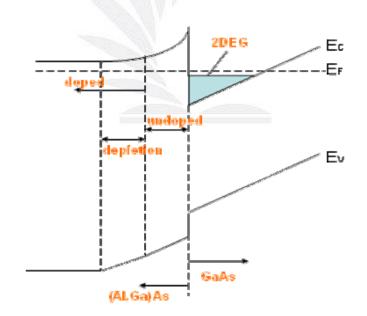

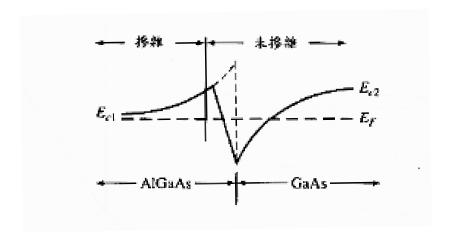

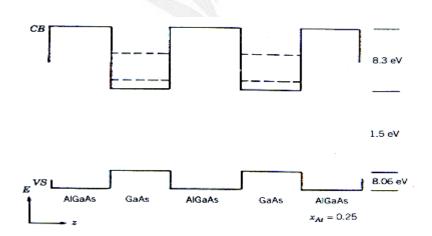

在1970年代後期,貝爾實驗室的實驗中發現一種以磊晶成長,具有二維電子氣(2DEG),由 undoped GaAs 和 n-doped AlGaAs 所組成的異質結構。這兩種材料有相同的晶格常數,因此形成一個晶格匹配的異質結構。如圖 1-1 所示砷化鋁鎵(AlGaAs)為寬能隙、砷化鎵(GaAs)為窄能隙的材料,當形成接面後,接面因為兩邊是異質的材料,能隙大小不同,因此能帶呈現不連續的情形。

圖 1-1 砷化鋁鎵/砷化鎵/砷化鋁鎵能帶圖

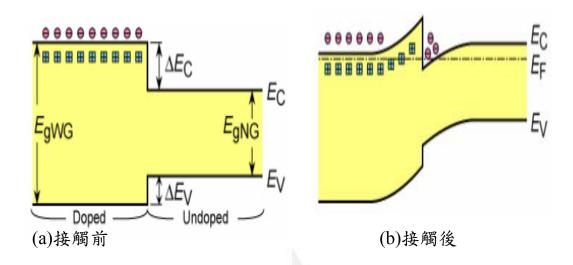

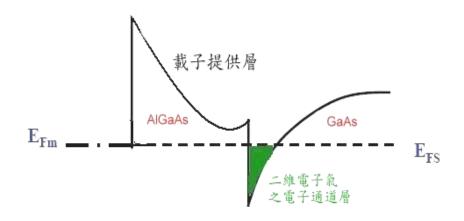

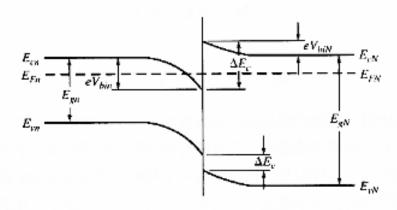

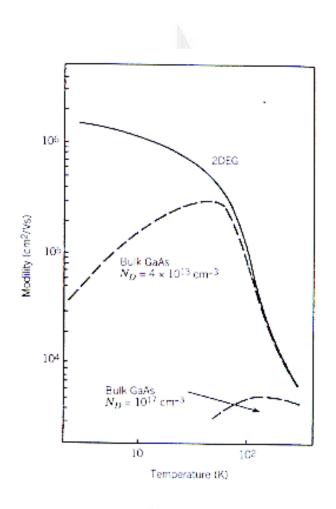

從圖 1-2 中顯示,若在砷化鋁鎵(AlGaAs)層上摻雜施體雜質以形成 N 型,寬能隙的砷化鋁鎵(AlGaAs)層上所游離的自由電子會大幅掉入窄能隙無摻雜的砷化鎵(GaAs)層中。這個轉移在異質接面建立一個電場和能帶彎曲,在接面、靠近窄能隙且高純度的砷化鎵處形成近似三角形區域的「二維電子氣」(2DEG)。被傳遞的電子被侷限在 GaAs 側上的窄能勢井,在此區域內能隙較小且濃度近於本質濃度,並且在空間上從施體離子分離出來。如此離子雜質散射將被大大地壓抑,此機制將形成高電子遷移率。

圖 1-2 HEMT AlGaAs/GaAs 異質結構能帶圖

以往金半場效電晶體(MESFET)因為雜質與自由電子為同一位置,因此若要提高自由電子密度而增加摻雜濃度,通道變成高濃度摻雜的砷化鎵,雜質散射會非常嚴重。高電子遷移率場效電晶體的自由電子則在高純度砷化鎵側形成的二維電子氣區域中做二維的運動(一為源極至汲極的方向、一為平行於通道的寬度通道寬度的方向),這是高電子遷移率場效電晶體高速的原因。

HEMT 設計的目標之一就是結合高電子遷移率 μ 與高 2DEG 電子體密度 n。之後發現,用 InGaAs 層替換 GaAs 層,μ\*n 的值可以大大地增加。因此為了要在材料上改進飽和速度,近來便開始積極發展砷化銦鎵(InGaAs)或磷化銦(InP)的應用。再者,由於砷化鎵金屬半導體場效電晶體(GaAs MESFET)運作時,必須提供兩個電壓來源,輸出功率與增益大小的效果較差,於是傳統的砷化鎵金屬半導體場效電晶體(GaAs MESFET)也逐漸被 HEMT 或 HBT 結構給取代。

#### HEMT 的元件結構發展

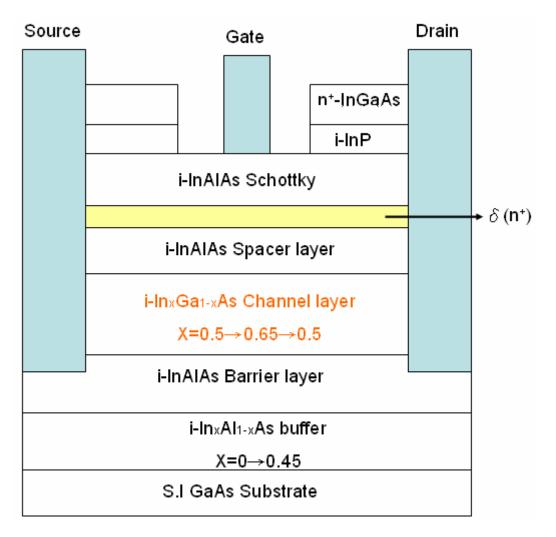

#### (1) Pseudomorphic HEMT (PHEMT):

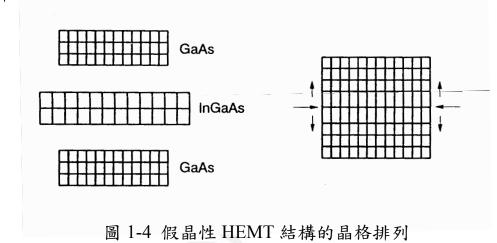

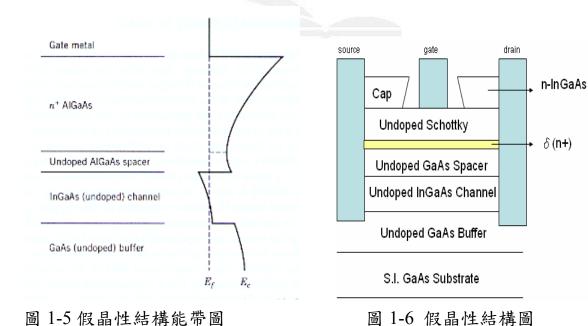

由於傳統的 GaAs 通道層,其 µ 不夠高,再加上載子的 侷限能力不夠強,所以便利用 InGaAs 為二維電子氣通道的 材料來改進 HEMT 的特性,但發現 InGaAs 與 AlGaAs 兩者 間晶格常數的差異,所以我們便製作一層薄的 InGaAs(In 的 莫耳分率大約在 0.25 左右),其厚度大約在 100Å 左右,使得 晶格與 GaAs 匹配。在圖 1-4 中可看出 InGaAs 為了匹配 GaAs 或 AlGaAs 的晶格常數而被壓縮。圖 1-5 與圖 1-6 為假晶性結構的能帶與幾何圖形。

圖 1-4 中 InGaAs 承受像一般方晶結構以四角形形式歪斜, InGaAs 與 GaAs 間有一個臨界厚度能允許晶格不匹配變形。當莫耳含量 In 與 Al 提高時,臨界厚度會變薄以至於量子尺寸影響而產生電子次能帶,實際上卻降低了電子的位能限制力。但 HEMT 中運用薄層 InGaAs 的好處包含增強電子的傳輸,改善載子在量子井中的限制力和有較高的電子移動率。

#### (2) InP HEMT:

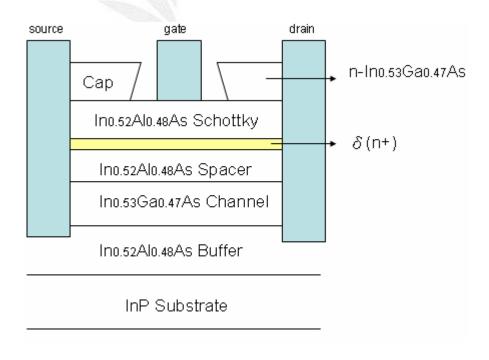

由於GaAs/InGaAs晶格常數不匹配,所以發展出以InP為基板的HEMT,由於通道中(材料通常為In<sub>x</sub>Ga<sub>1-x</sub>As)有較高的的銦(In)含量與InP晶格匹配時x約為 0.53,所以通道具有高電子移動率、高的飽和速度、低的電子有效質量,再許多應用上元件的性能都來得比GaAs系列優異許多(由於基格匹配的關係,通道的x不會超過 0.25),因此當應用在異質結構場效電晶體的通道層時,可以提升元件的傳輸速度,進而改善元件的高頻響應,以及增加通道載子的侷限能力。圖 1-6 是InPHEMT的簡圖

圖 1-6 InP HEMT 結構圖

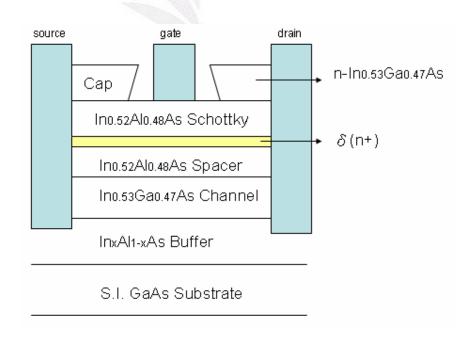

### (3) Metamorphic HEMT (MHEMT)

雖然以 InP 為基板的 HEMT 特性很好,但是由於 InP 的基板成本較高,且容易破碎,亦沒有較大尺寸的基板,使得在商業的應用上增加了其製成的困難度,也增加了其生產成本及費用。為了解決這些問題,便在 GaAs 基板上成長 InP 系統材料,此種變晶(metamorphic)方法,不但可以使元件保有 InP 的高性能特性,更可以利用較便宜且大尺寸的 GaAs 基板降低生產成本,因此是未來應用上的一大方向。圖 1-7 為 metamorphic HEMT 的結構圖。

圖 1-7 metamorphic HEMT

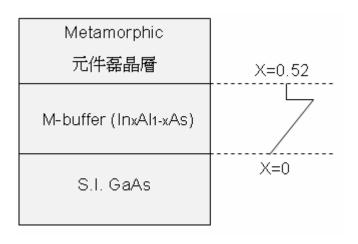

Metemorphic 最主要的目的在於可以在 GaAs 基板上成長錮(In)莫耳分率較高的 InxGa1-xAs 材料,使得元件的特性可以與成長在 InP 基板上匹敵。然而當 In 的含量越大,則 GaAs與 InGaAs 的晶格不匹配也越嚴重。當晶膜厚度大於零界厚度時,晶格間所存在的應力會使晶格發生扭曲進而引起晶格的缺陷及錯位,使元件的特性大幅的衰減。為了克服此問題,在磊晶成長變晶型元件時,必須在 GaAs 及 InGaAs 之間長一變晶緩衝層(metamorphic buffer)來釋放 GaAs 及 InGaAs 因晶格不匹配所造成的應力。所以如何成長高品質、高阻值、無缺陷的變晶緩衝層,將是決定元件特性優劣的主要關鍵。目前最常用的變晶緩衝層為逆向步階式漸進緩衝層(inverse step graded buffer),如圖 1-8

圖 1-8 metamorphic HEMT 漸進式緩衝層

因為砷化鋁(AlAs)的晶格常數與砷化鎵(GaAs)的晶格常數幾乎一樣,所以我們的變晶緩衝層可以在 GaAs 基板側成長 AlAs(即 InxAl1-xAs,其中 x=0),然後逐漸調變 In 和 Al 的成分,至 In0.52Al0.48As,因為此時的 In0.52Al0.48As 晶格常數與 InP 的晶格常數是相等的,不過在調變的過程中,我們會將 In 的含量先超過 0.53(通常會到 0.63),在降回至 0.52,形成所謂的逆向步階式漸進緩衝層。因為這樣能夠最有效釋放因晶格不匹配所造成的應力。

藉由調變 M-buffer 不同 In 的含量,我們可以隨意調整通道中 In 的含量,若要適用於高功率元件中,則元件之崩潰電壓必須要大,因此通道中的 In 的含量通常不超過 0.4。反之若要用於高頻率、低雜訊的放大器上,則元件必須有較大的電子移動率及轉導值,因此通道中 In 的含量通常在 0.5 以上。

綜合討論,而在主動元件方面,純矽製程的 CMOS 在閘極通道縮短的情況下,以目前的技術(0.18μm 或 0.25μm),約可使用到 5GHz 以下頻段的電路,更高的頻段需要 0.13μm 或更先進的製程。但若要求極佳線性度 CMOS 能然不能被應用超過 30GHz。雖然製程微縮可提高電流截止頻率及功率截止頻率,但其他參數急速惡化,除了使用矽絕緣層(Silicon on Insulator, SOI)改善基板損耗(substrate loss)之外,製程微縮帶來的不良影響仍無法避免。

雖然 Si MOSFETs 在許多電路設計已廣泛利用,但仍然 努力開發研究新的半導體材料,例如在高功率、高頻電路應 用中使用具有優秀電性 III-V 族化合物半導體材料。

高速及高功率元件積體電路興起並廣泛的使用,其中我們對高電子移動率電晶體(HEMT)作簡單的研究,在此我將分為其 HEMT 的工作原理、元件製程簡介、霍爾量側、精確量測元件的 S 參數,並且進行模擬,求得等效電路中本質與外質的元件值,以得到與電晶體製程相關參數以及建立高頻元件模型。

# 第二章 高電子移動率電晶體工作原理

## 2-1 工作原理

高電子移動率電晶體(HEMT)和雙極性異質接面電晶體 (HBT)是 III-V 族化合物半導體近代較成熟的元件,而元件的操作主要還是仰賴異質接面。元件中異質接面因有不同的主成成分及能隙產生,例如:GaAs/AlGaAs 或 InGaAs/InP。目前這些新發展的元件在微波和高速數位積體電路中比單一接面元件提供更好的電位特性。在 HEMT 中設計磊晶層結構是為了讓自由電子在通道中自己由施體離子中分開,進而改善基座的性能,遠比典型的 MESFETs 來的好。

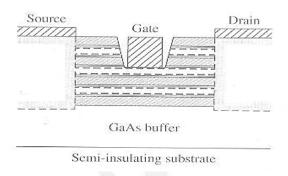

圖 2-1 基本 HEMT 幾何結構圖

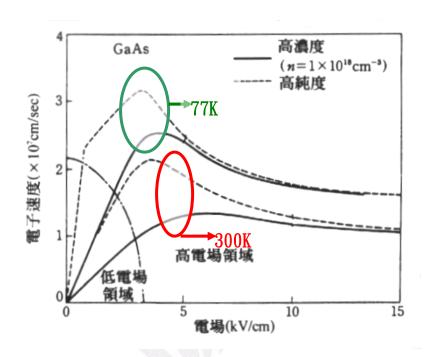

由 2-2 圖可看出電子速度在高純度砷化鎵比在高濃度摻雜的砷化鎵快。溫度若降到 77K,不論在高純度砷化鎵或在高濃度的砷化鎵,電子速度都比 300K 快。

圖 2-2 砷化鎵中電子速度與電場及溫度的關係圖

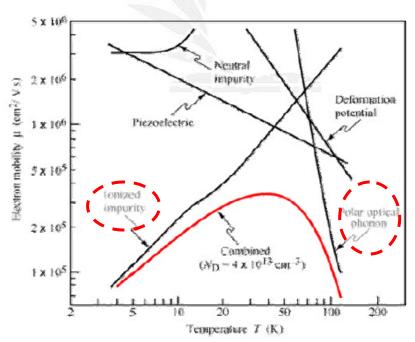

高純度砷化鎵中的電子在半導體中的電子遷移率主要 受兩種散射所影響:

### (1) 極性聲子散射 (polar optical phonon)

80K以上,晶格熱擾動嚴重,此時雜質散射也比較不明顯,因此溫度電子遷移率由晶格熱擾動引起的極性聲子散射所支配。

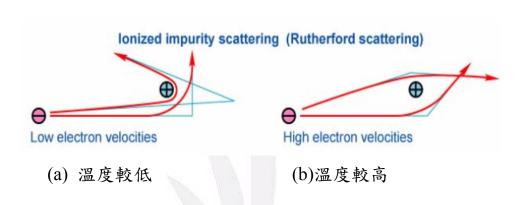

## (2) 雜質散射 (Ionized Impority)

40K以下,自由電子受施體雜質中正離子的靜電引力牽引 嚴重,此效應為「雜質散射」。如圖 2-3。

$$E_{kin} = \frac{1}{2}mv^2 = \frac{3}{2}kT \tag{2.1}$$

圖 2-3 電子受雜質散射

圖 2-4 高純度砷化鎵電子移動度與溫度及

各項散射因素對其的影響

藉由增大電子與解離施體雜質之間的間隔,雜質散射的效應還可以被進一部地降低。陡峭異質接面的位勢井之中的電子是與施體原子分離的,但是他們仍然還是足夠接近,因而可能還是會受制於庫倫吸引力。我們可以在摻雜的 AlGaAs與無摻雜的 GaAs 之間置放一層薄且未摻雜的 AlGaAs 隔離層 (spacer layer)。圖 2-5 顯示這個結構的能帶圖。增大載子與解離施體之間的間隔會使電子遷移率進一步上升,這是因為雜質散射降低(庫侖交互作用變低)。這種漸變異質接面的一項缺點乃是位勢井之中的電子密度會有比陡峭接面來得小的傾向。

圖 2-5 N型 AlGaAs-未掺雜 AlGaAs-未掺雜 GaAs 異質接面傳導帶邊緣

在 1981 年,典型 AlGaAs/GaAs 高電子移動率電晶體能提高速度,高增益及在微波元件有出色的功率特性。自從 1986年,假晶性結構 HEMT 發展的非常迅速。其中利用 InGaAs材料代替 GaAs 為二維電子氣 (2DEG)通道層能提高 HEMT以 AlGaAs/GaAs 為結構的特性。這個薄層 InGaAs 就像假晶性通道,能比 GaAs 層有更高的載子限制力,及在AlGaAs/InGaAs 異質接面中有優良的傳導特性,此異質接面允許較高片狀電荷密度。因此,比典型以 AlGaAs/GaAs 為結構的 HEMT 有較高的電流密度和轉導值。

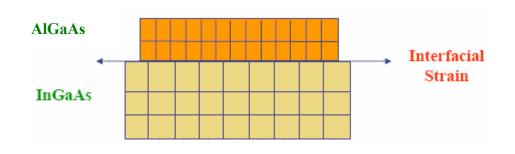

在 InGaAs 通道層與 AlGaAs 之間因為晶格不匹配, 圖 2-7,所以 InGaAs 層必須控制的很薄以至於晶格不匹配的 問題可以改善,成為一個必要的假晶性電子自由位移的材料。從前 InGaAs 層的厚度往往超過臨界厚度而造成晶格的位移,當為了維持晶格匹配把銦的掺雜濃度提高會使臨界厚度 下降,所以當注入高含量的銦時 InGaAs 層的厚度就必須設計的更薄。當我們提高銦的濃度時有包含以下幾點好處:

- (1)高電子移動率

- (2)高載子限制力

- (3)高電流密度

- (4)高轉導值

- (5)高單位電流增益頻率

- (6)低源極電阻值。

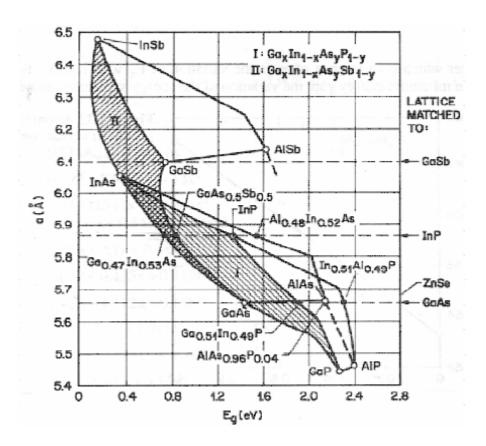

圖 2-6 Ⅲ- V族材料能帶對基格常數匹配圖

圖 2-7 AlGaAs/InGaAs 接面晶格不匹配

許多研究成果都在發展緩衝層,為了提高絕緣通道特性和消除在基板上造成的電性影響。典型未掺雜 GaAs 緩衝層電子會藉由 Drain(洩極)和 Source(源極)電場注入緩衝層,所以不能提供好的絕緣特性。但是預測有較高電阻係數和較大能隙的 AlGaAs 是一個理想的緩衝層材料。元件的性能與長晶參數有密切的關係,這也是為什麼難獲得較好介面品質的主要原因。介面品質不好造成電子移動率下降,其中要改善這個問題是插入 GaAs 薄層在粗糙的 AlGaAs 層中以增加雜質數目,並且提供下一層 AlGaAs 長晶層一個平滑的表面,這樣能阻絕來自基板因缺陷和雜質產生的電性影響,並且有精確的夾止特性和微波功率特性。

利用調變式 δ-摻雜層代替載子提供層去提升載子的濃度,進而提高電流密度和轉導值。使用不同閘極凹溝厚度去獲得不同蕭基層厚度,進而得到較好的直流特性。此外,溫度的變化量也是影響直流特性的因素之一。

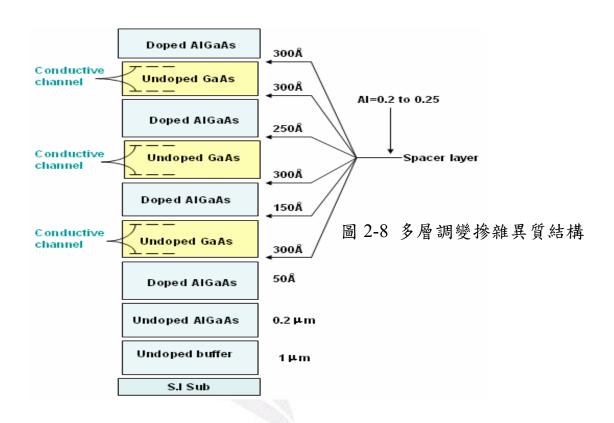

分子束磊晶(MBE)製程使元件可以成長非常薄的一層具有特定摻雜的特定半導體材料。特別是,如同圖 2-8 中所顯示,元件形成多層的調變摻雜異質結構,許多電子表面通道

層會被平行地形成。這種結構等同於將通道的電子密度增大,但會使 FET 的電流容量增大。

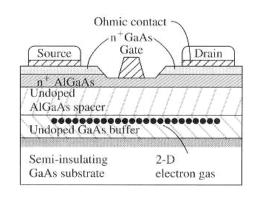

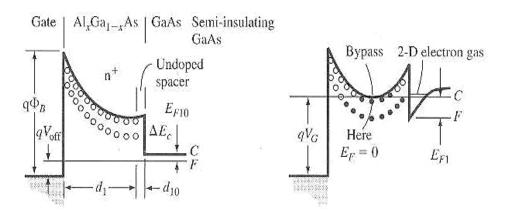

圖 2-9 中顯示一個典型的 HEMT 結構。N- AlGaAs 是藉由一層無摻雜的 AlGaAs 間隔層而與未摻雜的 GaAs 分隔開。在 N- AlGaAs 之上的一個蕭特基接觸構成了電晶體的閘極。這種結構是一個「正常」的 MODFET。圖 2-10 中則顯示一個「反轉」的結構。在這種情況之下,蕭特基接觸是製作在無摻雜的 GaAs 層之上。由於正常的結構可以得到較佳的結果,因此比較少研究反轉的 MODFET 結構。

圖 2-9 典型 AlGaAs-GaAs HEMT

圖 2-10 「反轉的」 AlGaAs-GaAs HEMT

元件可以經由閘極電壓來控制在位勢井之中的二維電子 氣中的電子濃度。

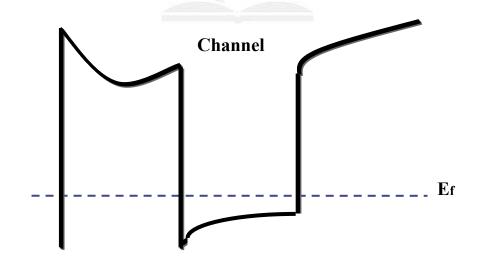

(1) 當具有零偏壓時,在GaAs之中的傳導帶邊緣比費米能階低,隱喻會有高濃度的二維電子氣,接面的能帶如圖 2-11 所示,此種元件通道層內原本就有電荷,具有臨 界電壓(V<sub>T</sub>)為負值,稱為空乏模式(常開型)高電子遷移 率場效電晶體。

圖 2-11 閘極加零偏壓時 AlGaAs 接面能帶圖

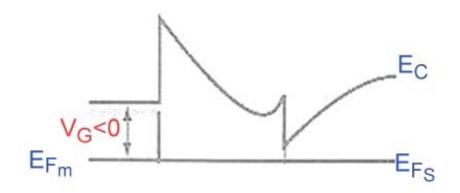

(2) 當有一個負電壓被外加至閘極時,在 GaAs 之中的傳導帶邊緣比費米能階高,蕭基閘極的電場會將位勢井之中的 二維電子氣層排除,因此二維電子氣之中的濃度是非常 低,而在一個 FET 之中的電流基本上是零。圖 2-12。

圖 2-12 閘極加負偏壓時 AlGaAs/GaAs 接面的能帶圖

蕭特基障礙由表面開始使 AlGaAs 層空乏,而異質接面則由異質接面界面處開始使 AlGaAs 層空乏。理想而言,應

該將元件設計得使兩個空乏區剛好重疊,以避免電子經由AlGaAs 層來傳導。對空乏模式的元件而言,由蕭特基閘極開始的空乏層應該只會延伸至異質接面的空乏層為止。對於增強模式的元件,摻雜 AlGaAs 層的厚度會比較少,而蕭特基閘極的內建位勢障礙會使 AlGaAs 層及二維電子氣通道都被完全地空乏。在一個增強模式的元件的閘極上外加一個正電壓會使元件導通。

在一個正常的結構之中,我們可以使用一個電荷控制模型(charge control model)來描述二維電子氣的濃度( $\mathbf{n}$ s)。

我們可以寫出

$$n_s = \frac{\mathcal{E}_N}{q(d + \Delta d)} (v_g - v_{off})$$

(2.2)

其中 $\mathcal{E}_{N}$ 是 $\mathbf{n}$ -AlGaAs的電容率, $d=d_{d}+d_{i}$ 則是摻雜加未 摻雜AlGaAs層的厚度,而 $\Delta d$ 是下式所給予的修正因數。

臨界電壓Voff是

$$V_{off} = \phi_B - \frac{\Delta E_c}{q} - V_{p2}$$

(2.3)

$$\Delta d = \frac{\mathcal{E}_N a}{q} = 80\mathring{A} \tag{2.4}$$

$$V_{p2} = \frac{q N_d d_d^2}{2 \varepsilon_N}$$

(2.5)

其中 $\Phi_B$ 特基障礙高度,而 $V_{P2}$ 的閘極偏壓將會使二維電子氣的濃度降低。如果外加一個正的閘極電壓,則二維電子的濃度將會增大。將閘極電壓增大會使二維電子氣的濃度增大,直到AlGaAs的傳導帶跨越電子氣的費米能階為止。圖 2-13 顯示這個效應。在這個點,由於在AlGaAs之中一條平行的傳導通道已經被建構起來,因此閘極喪失了對於電子氣的控制。

(a) 具有較小順向閘極電壓

(b)較大順向閘極電壓時,在 AlGaAs 中產生一條傳導道

圖 2-13 一個增強型 HEMT 能帶圖

HEMT也可以使用多種異質接面層來加以製造,這種元件形式顯示於圖 2-14 之中。一個AlGaAs—GaAs介面的單一異質接面具有一個在  $10^{12}$ cm<sup>-2</sup>階層的最大二維電子薄層濃度。

圖 2-14 多層 HEMT 結構

我們可以藉由在相同的磊晶層之中製造兩個或更多個AlGaAs—GaAs 介面來使這個濃度增大。元件的電流容量會被增大,而功率績效也會改善。多通道 HEMT 的表現就如同多個單一通道 HEMT 被並聯連接,並以相同的閘極來加以調變,但卻會具有稍微不同的臨限電壓。由於每一條通道的臨限電壓會改變,因此最大的轉移電導並不會隨著通道的數目而直接地縮小放大。此外,當閘極與通道之間的距離增大時,等效通道長度也會增大。當通道長度縮短時,最大頻率會增大。具有 0.25µm 通道長度的 HEMT 已被量測具有在 100GHz 階層的截止頻率。

在 HEMT 中可以獲致較高的操作速度,較低的功率發散,及較低的雜訊的觀點而論,HEMT 本質上便比其他的 FET 技術來得優秀。這些優點是直接來自於藉由使用未摻雜的 GaAs 來作為 FET 的通道層所獲得的優異傳輸性質。如同先前所說明已經發現,在一條無摻雜的通道之中獲致適宜的載子濃度的一種方法乃是在一個半導體異質接面的界面處使載子堆積。HEMT 的缺點乃是異質接面的製造程序會比較複雜。

以上是對 HEMT 基本原理的討論。接下來在下列章節中將介紹 HEMT 結構中二維電子氣(2-DEG)、夾止電壓與轉移電導基本原理等特性。在第三章介紹磊晶成長技術MOCVD(金屬有機化學氣象沉積)系統、MBE(分子束磊晶法)、參數和長晶步驟,以及二維電子氣、夾止電壓、轉移電導和元件製程設計結構包含晶圓定位、高台絕緣和金屬化閘極。並且在3-4節元件特性量測中提到霍爾量測和元件I-V特性討論。

### 2-2 二維電子氣

在考慮異質接面的靜電學之前,將先討論同型接面的一項獨特的特性。圖 2-15 顯示一個 n-N GaAs-AlGaAs 異質接面在熱平衡時的能帶圖。

圖 2-15 pn 異質接面在熱平衡下的能帶圖

AlGaAs可以是適度掺雜至重掺雜的 n型,而 GaAs可以是較輕摻雜,或者甚至是本徵的。如同之前所提及的,為了獲致熱平衡,電子會由寬能隙 AlGaAs 流動進入 GaAs 之中,而在鄰近界面處的位勢井之中形成一層電子的堆積層。我們之前已經發現的一項基本量子學的結論乃是,被侷限於位勢井之中的一個電子在一個(垂直於介面的)空間方向上具有量子化的能量,但卻可以在其它兩個空間方向上自由移動的這種情況。

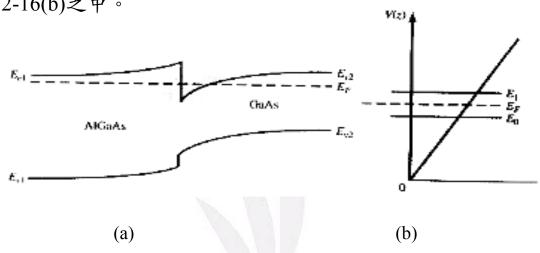

接近界面的位勢函數可以以一個三角形的位勢井來加以 近似。圖 2-16(a)顯示接近陡峭接面的界面處的傳導帶邊緣, 而圖 2-16(b)則顯示三角形位勢井的近似。可以使用這個位勢 函數來求解薛丁格波動方程式,量子化的能階顯示於圖 2-16(b)之中。

圖 2-16 (a) N-AlGaAs - i-GaAs 異質接面傳導帶邊緣

(b) 具有離散電子能量的三角形位能近似

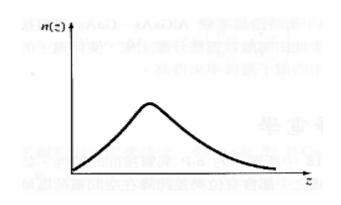

圖 2-17 之中顯示電子在位勢井之中分部的定性描述。與 界面平行的電流將會是電子濃度與電子移動率的一個函數。 由於 GaAs 可能是輕摻雜或者可能是本徵的,因此二維電子 氣勢在一個低雜質摻雜的區域之中,這使得雜質散射效應會 被極小化。電子的遷移率會比假設電子與解離施體都是在相 同的區域之中的情況大很多。

圖 2-17 三角形量子井中的電子濃度

$$V(z) = eEz \quad z > 0 \tag{2.6a}$$

$$V(z) = \infty \qquad z < 0 \tag{2.6b}$$

與界面平行的電子移動仍然還會受到AlGaAs之中解離 雜質的庫倫吸引力的影響。藉由使用一個漸變 AlGaAs-GaAs 異質接面,這些力量的效應可以被進一步地降低。漸變層是 Al<sub>x</sub>Ga<sub>1-x</sub>As,其中莫爾分量x會隨著距離而改變。

在這種情況之下,一層本徵的漸變 AlGaAs 被包夾在 N型 AlGaAs 與本徵的 GaAs 之間。圖 2-18 顯示熱平衡時跨越漸變 AlGaAs-GaAs 異質接面的傳導帶邊緣。位勢井的電子會進一步地由解離雜質被分離出來,使得電子的遷移率增大,並且會比陡峭異質接面之中的電子遷移率來的高。圖 2-19 低電場中摻雜濃度與 2-DEG 中移動率關係圖

圖 2-18 漸進異質接面處的傳導帶邊緣

圖 2-19 低電場中摻雜濃度與 2-DEG 中移動率關係圖

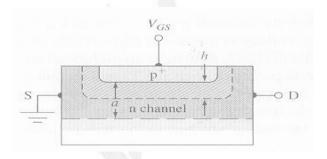

在討論夾止電壓時,圖 2-20 顯示一個簡化的單邊n通道 pn  $JFET。在p^+ 閘極區域與基板之間的冶金通道厚度是a,而單邊p^+ n 接面的感應空乏區寬度是h。假設洩極-至-源極電壓是零。如果假設陡峭空乏近似,則空間電荷寬度是$

$$h = \left\{ \frac{2\varepsilon_s (V_{bi} - V_{GS})}{eN_d} \right\}^{1/2} \tag{2.7}$$

其中 $V_{gs}$ 是閘極-至-源極的電壓,而 $V_{bi}$ 是內建的位勢障礙。對

一個逆向偏壓的 $p^{\dagger}n$  接面而言, $V_{gs}$ 必然是一個負的電壓。

圖 2-20 n 通道 pn 接面 FET 簡化幾何圖形

在截止時,h=a ,而跨降在接面上的總位勢稱為內部夾止電壓(internal pinchoff voltage),以 $V_{po}$ 來加以表示。結果將得到

$$a = \left\{ \frac{2\varepsilon_s V_{po}}{eN_d} \right\}^{1/2} \tag{2.8}$$

$$V_{po} = \frac{ea^2N_d}{2\varepsilon_a} > 0 \tag{2.9}$$

注意內部夾止電壓被定義為一個正的數量。

內部夾止電壓並不是獲致夾止時的閘極-至-源極電壓。為了獲致夾止,必須外加的閘極-至-源極電壓稱為夾止電壓(pinchoff voltage),也稱為關閉電壓(turn-off voltage)或臨限電壓(threshold voltage)。夾止電壓是以符號 $V_p$ 來表示,並且是以方程式(2.7)以及(2.8)來加定義

$$V_{bi} - V_p = V_{po} \quad \text{is} \quad \boxed{V_p = V_{bi} - V_{po}} \tag{2.10}$$

在一個n通道空乏模式HEMT之中,獲致夾止的閘極-至-源極電壓是一個負值,因此 $V_{po}\!>\!V_{bi}$ 。

在本節中也討論在 HEMT 中重要的參數-轉移電導。轉 移電導是電晶體增益,它表明閘極電壓對於洩極電流的控制 能力。轉移電導被定義為

$$g_m = \frac{\partial I_D}{\partial V_{GS}} \tag{2.11}$$

使用上一節之中所推倒得到的理想洩極電流的表示式,可以寫出轉移電導的表示式。

一個 n 通道空乏模式的元件在不飽和區域之中的洩極電流,在相同的區域之中,我們可以決定電晶體的轉移電導是

$$g_{mL} = \frac{\partial I_{D1}}{\partial V_{GS}} = \frac{3I_{p1}}{V_{po}} \sqrt{\frac{V_{bi} - V_{GS}}{V_{po}}} \left\{ \sqrt{\left(\frac{V_{DS}}{V_{bi} - V_{GS}}\right) + 1} - 1 \right\}$$

(2.12)

取Vns變成非常小的極限,轉移電導會成為

$$g_{mL} \cong \frac{3I_{p1}}{2V_{po}} \cdot \frac{V_{DS}}{\sqrt{V_{po}(V_{bi} - V_{GS})}}$$

(2.13)

可以將上式以電導參數Go來加以表示為

$$g_{mL} \cong \frac{G_{01}}{2} \cdot \frac{V_{DS}}{\sqrt{V_{po}(V_{bi} - V_{GS})}}$$

(2.14)

在飽和區域之中,發現在飽和區域之中的轉移電導是

$$g_{ms} = \frac{\partial I_{D1}(sat)}{\partial V_{GS}} = \frac{3I_{p1}}{V_{po}} \left[ 1 - \sqrt{\frac{V_{bi} - V_{GS}}{V_{po}}} \right] = G_{01} \left[ 1 - \sqrt{\frac{V_{bi} - V_{GS}}{V_{po}}} \right]$$

(2.15)

使用方程式(2.16)所給予的電流-電壓近似,並將轉移電導寫成(2.17)式

$$I_{D} = I_{DSS} \left( 1 - \frac{V_{GS}}{Vp} \right)^{2}$$

(2.16)

$$g_{ms} = \frac{-2I_{DSS}}{V_p} \left( 1 - \frac{V_{GS}}{V_p} \right) \tag{2.17}$$

由於n 通道 JFET 的 $V_p$  是負的,因此 $g_m$  是正的。

# 第三章 元件製程與特性量測

近年來,高電子移動率電晶體被引起注意因為下列幾個優點:

- (1)高電子移動率

- (2)較低成本消費

- (3)高單位電流增益頻率

- (4)高崩潰電壓與高功率特性

| )                     | GaAs |        |     | Silicon |      |

|-----------------------|------|--------|-----|---------|------|

|                       | HEMT | MESFET | HBT | BJT     | CMOS |

| Speed                 | 1    | 3      | 2   | 4       | 4    |

| 速度                    |      | ( P    |     |         |      |

| Lithography           | 2    | 3      | 1   | 1       | 4    |

| requirements 微影條件     |      |        | 6   |         |      |

| Processing complexity | 2    | 1      | 4   | 3       | 3    |

| 製程複雜度                 |      |        |     |         |      |

| Material problem      | 4    | 3      | 4   | 1       | 1    |

| 材料問題                  |      |        |     |         |      |

| Power-delay product   | 1    | 2      | 4   | 1       | 1    |

| 功率-延遲 乘積              |      |        |     |         |      |

表 3-1 各元件特性比較量表(1=出色;4=較差)

由表 3-1 可以知道 HEMT 整體而言,明顯比其他積體電路製程元件優秀,例如在速度比較上 CMOS 和 BJT 就顯的較為遜色以及製程複雜度上 HBT 更為困難。

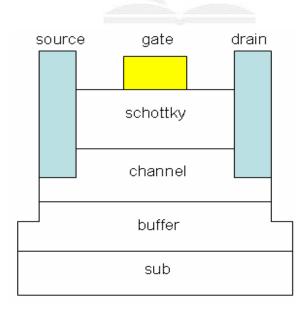

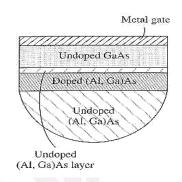

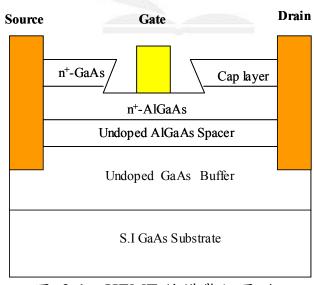

典型高電子移動率電晶體結構設計如圖 3-1。想要順利的操作HEMT,關鍵就在於從施體(離子原子)中分離出電子,此時必然同時在AlGaAs/GaAs這兩個不同材料層因為有不同的的電子親和力,所以異質界面處有電流產生。因為位能井的寬度比德布羅依波長小,2-DEG二維電子氣被限制在內部的三角位能井中,並且電子能帶會被量子化。典型AlGaAs/GaAs HEMT 結構把N<sup>+</sup>GaAs設計成覆蓋層,AlGaAs蕭基層,GaAs通道層和GaAs緩衝層。

圖 3-1 HEMT 結構幾何圖形

在製程的演進下,要提高電流截止頻率及功率截止頻率的方式有二種選擇:一是縮短閘極通道程度(gate length scale down),另一則是提高飽和速度( $V_{sat}$ )。高電子遷移率場效電晶體直流增益轉導( $g_m$ )及電流截止頻率( $f_T$ )的表示式如 3-1、3-2 式:

$$f_{\rm T} = \frac{v_{sat}}{2 \pi L_{g}} \tag{3.1}$$

$$gm = \frac{v_{sat}}{2\pi C_{es}}$$

(3.2)

其中Vs為電子飽和速度、Lg為閘極長度

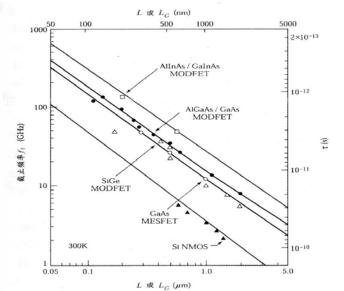

- (1) 縮短閘極通道程度(gate length scale down),製程技術的 因素,圖 3-2 為各種場效電晶體電流截止頻率對閘極長 度的關係圖。

- (2) 提高電子飽和速度(Vsat),材料特性的因素。 而由(3.2式)知電子飽和速度(Vsat)對於提高直流增益 轉導也會有所助益。

圖 3-2 電流截止頻率 對閘極長度的關係圖

大學學生報告 ePaper(2005 年)

### 3-1 元件的基本結構

把 HEMT 元件結構做了一些改變包含使用漸變式 δ-摻 雜技術,假晶性 InGaAs 通道層和 AlGaAs/GaAs 超晶格緩衝 層。我們的設計為:

- (1) GaAs 覆蓋層

- (2) 未摻雜 AlGaAs 蕭基層

- (3) δ-摻雜層

- (4) 未摻雜 AlGaAs 隔離層

- (5) 未摻雜假晶性 InGaAs 通道層

- (6) 未摻雜 AlGaAs/GaAs 超晶格緩衝層

#### 3-1-1 覆蓋層

通常GaAs 覆蓋層是矽的重摻雜 大約是  $10^{18}$ cm<sup>-3</sup>,能在 HEMT中提供好的歐姆接觸。覆蓋層中高摻雜濃度和厚度使 得元件Source源極電阻值下降,並且保護了下一層蕭基層表面氧化作用。若是在閘極上沒有好的覆蓋凹槽層,將會導致 並聯的效應。

#### 3-1-2 蕭基層

蕭基層通常使用比通道層更寬能隙的材料,因為在AlGaAs/GaAs 異質接面傳導帶不連續,自由電子會以二維電子氣形式從 AlGaAs 擴散至 InGaAs,而 2-DEG 允許高薄電荷密度,必且改善載子限制力.在使 AlGaAs 蕭基層變薄時,問題是閘極金屬和通道層距離變小造成高轉導值,但也降低了崩潰電壓值。

### 3-1-3 δ-掺雜載子提供層

可以由妨礙長晶步驟中了解 $\delta$ -摻雜。切斷在長晶步驟時流動源 $A_sH_3$ 和 $S_iH_4$ 其中 $AlmGa的來源。因此,可以得到從側面急劇的摻雜。 薄層<math>\delta$ -摻雜製程在HEMT的好處為:

- (1)高洩極(drain)電流特性

- (2)低雜質散射效應

- (3)高轉導值

- (4)降低短通道效應

因為有高摻雜濃度,δ-摻雜材料有高汲極電流特性。在 五族元素位能井中載子被限制,所以明顯轉導值可以提高, 而直接影響短通道效應特性是因為閘極長度低於 2μm。由以 上說明我們知道  $\delta$ -摻雜技術在高速元件上有好的應用,因為有高電子移動率高載子濃度和高轉導值。庫倫位能井核能障外型改變,並印此改變量子能階。圖 3-3 為各種影響在能帶中的改變。

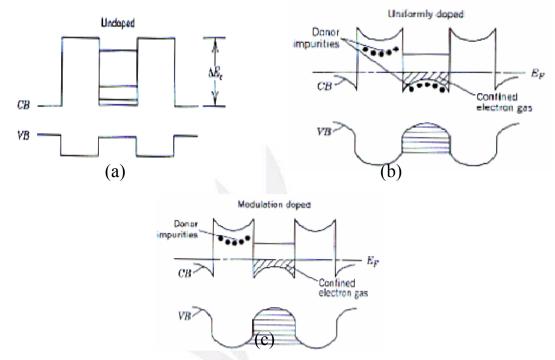

圖 3-3 施體與電子狀態在(a)非摻雜 (b)一般摻雜 (c)重摻雜能帶圖

#### 3-1-4 隔離層

在載子提供層與通道層間有兩個隔離層,隔離層主要是從接面施體離子分離二維電子氣,進而減少由施體原子庫倫散射的影響,提升電子移動率。而隔離層的厚度對電晶體特性有很重要的影響,較薄的隔離層厚度可在 InGaAs 通道中有效增加總電荷密度,換句話說,較厚的隔離層會提升電子的

移動率,但也降低電子在二維電子氣的傳導效率。典型的隔離層厚度在 20Å~50Å。

### 3-1-5 假晶性 InGaAs 通道層

利用 InGaAs 作為通道,因為傳統的 GaAs 通道的 μ不夠高,再加上載子的侷限能力不夠強,所以我們改用摻雜銦(In)的 InGaAs 為通道層,因為有參雜銦(In)所以元件的特性會大幅提升,在之前的章節有提過,最主要的原因是因為電子移動率(μ)的上升,而帶動其他的特性。

但是因為 InGaAs 與 GaAs 晶格常數不匹配,使得 In 的 摻雜量不可以太濃,所以通道層的厚度也很薄,讓 AlGaAs/InGaAs/GaAs 的晶格看起來類似於晶格匹配,這種做 法的名稱我們便稱為假晶性(Pseudomorphic)通道層,又稱作 Pseudomorphic HEMT (PHEMT)。

#### 3-1-6 緩衝層

為了有好的絕緣通道和排除從基板產生的電性影響,許 多的研究都在設法改進緩衝層結構。典型未摻雜 GaAs 緩衝 層雖然有很高的阻抗,但不良的基板品質卻不能有好的絕緣 系統。電子會藉由洩極-源極電場注入 GaAs 緩衝層。具有高 阻抗和寬能隙的 AlGaAs 是目前推測維理想的緩衝層材料, 而此元件特性與長晶參數息息相關,這也是為什麼很難得到 好品質接面的主要原因。為了改善不良接面使通道中移動率 降低的問題,其中能緩解此問題的技術是在 AlGaAs 層中插 入薄層 GaAs ,提高雜質濃度並在下一個 AlGaAs 長晶前產 生一個平滑的表面。此技術有效阻絕從基板產生的雜質和電 性,元件會有較好的夾止與微波功率特性。圖 3-4 為 AlGaAs/GaAs 異質結構的能帶圖。

圖 3-4 異質結構 AlGaAs/GaAs 能帶圖

### 3-2 磊晶成長技術

屬氣相磊晶做介紹。

砷化鎵IC製造過程中「磊晶」是相當重要的技術,分子 束磊晶(Molecular beam epitaxy,MBE)與金屬有機化學氣相沉 積(Metal-organic chemical vapor deposition,MOCVD) 因為能成長異質結構且具有大面積磊晶的能力因此成為目前

微波元件磊晶技術主流,以下分為針對分子束磊晶與有機金

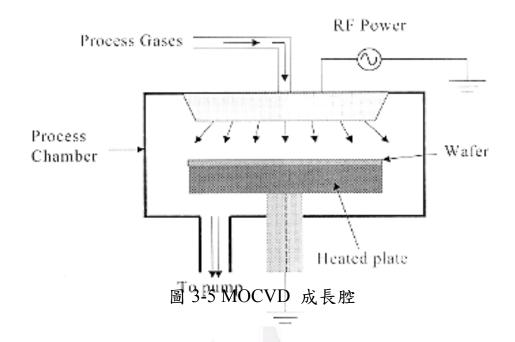

## 3-2-1 金屬有機化學氣相沉積(MOCVD)

目前在光電半導體元件發展,主要的應用有光通訊,包含光發射器-Laser diode。 LED 與光感測器-PIN、APD.以及高速電晶體,例如:FET、HEMT、HBT,其他如 NIPI...上述元件對材料的要求與趨勢為材料種類愈來愈多,如GaAs,InP,InGaAs,InGaP,InGaAsP,II-V之ZnS,ZnSe等。並且結構愈趨複雜、雜質純度要求提高、厚度控制愈來愈薄和尺寸愈來愈小,如:Quantum well,Quantum wire,Quantum dot ...。MOVCD 能符合上述要求,因此被廣泛應用。以下我們對 MOCVD 作詳細的介紹:

#### MOCVD 系統介紹

- (1) 原料部分:氫化物氣體均裝入高壓網瓶,經壓力調整器 降壓後,由流量控制器設定流量,流入反應腔.有機金 屬幾乎是以液態存於鋼瓶中,由溫度及載送氣體(H<sub>2</sub>) 精密控制適量送入 reactor。

- (2) 氣體處理部份:含開關、控制閥、流量計、排放管等。 將所有原料在量上作精密控制送入反應腔或排放管, 對晶膜之組成濃度,後度達到所需求之規格。

- (3) 反應腔部份:反應腔有垂直式、煙囪式、水平式及桶狀 式等。內有石墨材質之載物架放置基板,生產面積及 均勻性是其規格要求。

- (4) 電力及控制部分:反應腔為冷管式,用 RF 感應加熱, 溫度由 thermocouple 控制可電腦化。

#### MOCVD 生長過程

生長過程是將反應原料由氣相擴散或對流穿過邊界層 (Boundary layer)達到基板表面。若基板表面反應速率夠快,生長速率由反應物到達基板表面之量決定,增加反應物濃度就增加生長速率,此為 Mass transfer controlled 或 Diffusion controlled 操作。生長速率由反應物濃度決定時,對生長溫度不敏感,當反應物濃度在基板表面增加到超過基板反應速率,則生長速度由基板表面反應速率決定,此為 surface reaction controlled 或 kinetics controlled,生長溫度決定生長速率。

#### MOCVD 系統應用

MOCVD 是目前商用上最受歡迎的磊晶方法,因為:

- (1) 有機金屬原料有多重選擇,且純度、來源、價格、穩 定度及處理方便性都較 Halid CVD 為佳。

- (2) 不需高真空,系統價格低,維修容易。

- (3) 不需要溶劑(與 LPE 比較)。

- (4) 磊晶膜表面平滑,多重結構生長控制容易,Doping 易控制。

- (5) 可量產。

MOCVD(Metal Organic Chemical Vapor Deposition)又稱 OMVCD 或 MOVPE 或 OMVPE。MO(Metal-Organic)或 OM (Organo-metallics)在化學上 MO 係指金屬連接一個氧、硫、氮或磷原子,再轉接一個或多個碳原子;而 OM 是金屬原子直接接到一個或多個碳原子。

MOCVD使用有機金屬原料之蒸氣內所含的無機成分來 生長薄膜的一種氣相沉積技術。有機金屬原料中之有機部份 (含碳部分)決定其蒸氣壓之大小,分解難易和分解產物等, 在MOCVD流行之前,最常用的生長GaAs技術為鹵化物氣相 沉積法(Halide CVD) 其使用鎵元素為鎵原料,使用三氯化砷 (AsCl<sub>3</sub>)或砷化元素為砷化原料。為了使非氣態的鎵能由原料 區進入生長區,將鹽酸氣(HCl(g))與鎵反應產生氣態的氯化鎵 (GaCl)以便傳送主生長區,再與砷反應,即得GaAs film, Halid CVD 仍有下列缺點:

- (1) 至少須二個高溫區,溫度控制不易。

- (2) 反應釋放熱反應,故需用熱管式系統.反應腔石英管之腐 蝕污染不易防止。

- (3) 反應式均是可逆反應,故生長參數之控制相當困難,任 一參數之改變,均可導致蝕刻而非成長。

- (4) 大量載運氣體不被允許,因會將 HCI 吹至沉積區 (HCI 為酸性會蝕刻)導致蝕刻,若蝕刻速率>沉積速率。則成長轉成蝕刻,Halid CVD 是接近平衡點之放熱反應,成長參數需嚴格控制,而 MOCVD 則可離開平衡點甚遠之吸熱反應,可去除上述缺點。

### 3-2-2 分子束磊晶(MBE)

分子束磊晶是一種高精度的單晶薄膜生長技術,對於半 導體製程技術是相當重要的一項發展,它是在 1970 年代初 期,由貝爾實驗室的 John Arthor 及華裔的卓以和博士共同發 展出來的。近年來迭有提昇,不但可成長高品質且高純度的 磊晶層,對於量子井(Quantum well)、單原子層摻雜(δ-doping) 及超晶格(Superlattice)...等薄層結構,提供所需的準確厚度與 摻雜濃度控制,對於異質接面的成長控制也是之前磊晶法無 法比擬的,因此成為微波元件磊晶的主流技術之一。

### 分子束磊晶系統介紹

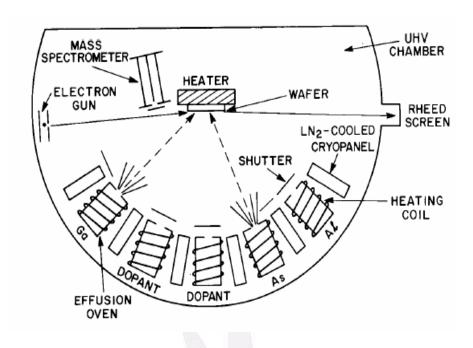

如圖 3-6 所示為分子束磊晶系統,以下簡述各系統的功 能與作用:

(1) 原料部分:典型的有 Al、As、Be(P型摻雜)及 Ga、In、Si(N形摻雜)面對基板做為元素源,元素源的爐口有快門(shutter)控制開關,蒸鍍的速率由爐管的溫度所控制。因為成長時會有高溫,所以必須藉由水或異丙醇循環以冷卻爐管。

- (2) 磊晶成長速度:典型成長 InGaAs、AlGaAs、GaAs 磊晶層速度為 0.5~1μm/h 之間,過多的 As 通亮並不影響 磊晶速度。一般而言,As 對 Ga 的比例必須維持在 20 左右,以避免形成 Ga 過多的表面。

- (3) 分子東通量監視器與基板加熱器:每一次成長前,每個元素源的通道會由基板背面的分子東通量監視器 (Beam flux monitor)測量。在材料成長前,基板會藉由基板加熱器(Substrate heater)加熱到接近 600℃。另外為了使磊晶薄膜的化學組成及厚度均勻,基板的承載座(Substrate holder)必須以垂直基板表面的方面不斷的旋轉,通常基板的承載座以大約 7.5rpm 的速度旋轉。

- (4) 反應式高能量電子繞射儀:反應式高能量電子繞射儀 (Reflection high energy electron diffraction,RHEED)利 用能量為5~50keV的電子束入射試片表面以偵測試片表面的原子結構,藉以得知試片的磊晶情形與清潔度。

- (5) 質譜儀: 質譜儀(Mass spectrometer)用來偵測異質氣體

量如 $H_2O \cdot O_2 \cdot COQN_2$ ,是在可忍受的範圍內。

圖 3-6 分子束磊晶系統示意圖

#### 分子束磊晶生長過程

先將待成長的晶片放置在一個超高真空(~10<sup>-10</sup>mmHg)的 反應室(chamber)中,所需成長的材料則放在反應室一端的 爐管中。當爐溫升至一定溫度時,爐中的材料會以原子東或 分子東的形式蒸發出來,此時基板也被加熱至一適當的溫 度。當分子東射至基板時,就會與基板表面的原子結合而形 成磊晶。磊晶成長的速率完全由單位時間內射到基板表面的 分子數目決定,這可以很容易的由裝置成長材料爐管的爐溫 所控制,一般成長的速率約為一秒鐘成長 0.1 層至 3 層原子。 由於速度慢,所以可以很精確的控制磊晶層的厚度。每個爐管的前端有一快門控制開關,決定磊晶層的起始點和終止點,控制這些開關的順序就可以得到多層的磊晶結構。

分子束磊晶技術的發明將半導體元件帶入一個嶄新的領域。過去元件的大小用微米(10<sup>-6</sup>m)計算,以分子束磊晶技術所作出來的元件大小則可用埃(10<sup>-10</sup>m)來計算,我們甚至可以準確到用原子的層數來計算磊晶的厚度。當這些磊晶層薄到約100Å時,傳統分析電子運動的方式已不再適用,而必須考慮到量子效應。

|       | 分子束磊晶 | 有機金屬氣相磊晶 |

|-------|-------|----------|

|       | MBE   | MOCVD    |

| 技術層次  | 中高    | 高        |

| 量產能力  | 低     | 中        |

| 磊晶成長速 | 中、低   | 中        |

| 度     |       |          |

| 成長極薄磊 | 容易    | 容易       |

| 臣     |       |          |

| 磊晶純度  | 追     | 高        |

| 磊晶平整度 | 好     | 好        |

|       |       |          |

表 3-2 MBE 與 MOCVD 比較表

### 3-3 元件的製程

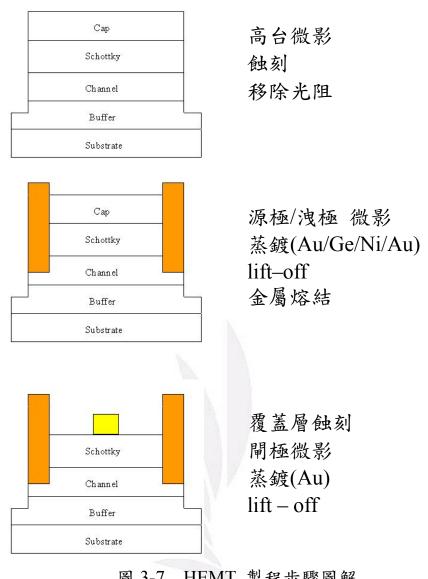

在製程時使用標準微影和 lift-off 技術來建立製程圖案 樣本的,必須在每個製程步驟前用丙酮加入超音波震動器清 洗,再用去離子水洗滌晶圓片,並用高純度氮氣吹乾以維持 晶圓片清潔.如圖 3-5 製程過程有以下四個步驟:

- (1)樣本定位

- (2)Source(源極)和 Drain(洩極)金屬化

- (3)高台絕緣

- (4) 閘極蕭基接觸

### 3-3-1 樣本定位

閘極方向必須平行橢圓形主軸去防止 lift-off 製程時產生開路現象。這也是為什麼選擇閘極為(100)方向,並且在高台蝕刻選用(011)方向,

| Сар       |  |

|-----------|--|

| Schottky  |  |

| Ch ann el |  |

| Buffer    |  |

| Substrate |  |

樣本定位 清洗晶片

HEMT 製程步驟圖解 圖 3-7

#### Source(源極)和 Drain(洩極)金屬化 3-3-2

利用丙同加入超音波震盪器中清洗晶圓並用氨水溶液 (NH4OH:H2O = 1:1)去移除氧化層表面。晶圓被 AZ1400 光 阻覆蓋均勻後在90度下30分鐘,之後則是利用標準的微影 製程定義出洩極和源極的圖形。蒸鍍的金屬與覆蓋板必須用

丙酮和鹽酸在超音速震盪器中清洗 20 分鐘後,用去離子水洗滌並用高純度氮氣吹乾.在源極和洩極的連接金屬是利用合金 Au/Ge/Ni 在事先蒸鍍的 Au 上,為了就市減少連接的電阻值。Lift-off 步驟是為了讓圖案和樣本間在快速熱退火中有好的熔結,使其有好的歐姆接觸特性。而主要源極和洩極金屬化步驟如下:

- (1)烘烤

- (2)上光阻,旋轉使覆蓋光阻均匀

- (3)軟烤(曝光前烘烤)

- (4)曝光

- (5)顯影

- (6)蒸鍍

- (7)Lift-off

- (8)合金連接

### 3-3-3 高台絕緣

高台絕緣的目的在於減少漏電流產生。若是能減少漏電流量,元件可以得到較好的夾止特性。在晶圓片上覆蓋均勻 AZ1400 光阻,把高台圖案微影至樣本上,再利用化學濕蝕刻。在 GaAs ,AlGaAs 和 InGaAs 各層中蝕刻溶液  $H_3PO_4$  :  $H_2O_2$  :  $H_2O=1$  : 1 : 30 。

必須確保元件高台蝕刻至緩衝層或基底層,為了有準確的蝕刻速率,利用γ波探測蝕刻時間與深度間的關係。而高台蝕刻的主要步驟如下:

- (1)烘烤

- (2)上光阻,旋轉使覆蓋光阻均匀

- (3)軟烤(曝光前烘烤)

- (4)曝光

- (5)顯影

- (6)硬烤

- (7)蝕刻

- (8)移除光阻

### 3-3-4 閘極蕭基接觸

在閘極金屬蒸鍍前,必須利用蝕科技術先移除覆蓋層。若是沒有完全移除乾淨,則會有並聯效應產生。運用源極和洩極為閘極光罩,所以並不需要運用到光學微影製程。再利用Au蒸度在AlGaAs上,形成蕭基接觸。在lift-off步驟後,場效電晶體元件算是完成。而閘極蕭基接觸主要步驟與源極和洩極金屬化步驟大致相同,只是少了合金連接的步驟。

### 3-4 元件的特性與量測

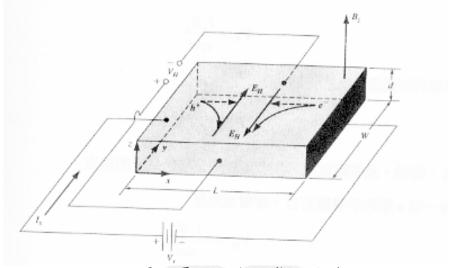

#### 3-4-1 霍爾量測

霍爾效應(Hall effect)乃是電場與磁場力量作用於移動電 荷時所得的結果。霍爾效應可用以鑑別下列元件特性:

- (1) 半導體是 n 型抑或是 p 型

- (2) 量測多數載子的濃度

- (3) 多數載子的遷移率

在此所討論的霍爾效應元件則是藉以由實驗來量測半導 體的參數。然而,這個元件也被廣泛使用於工程應用之中來 作為一個磁性探針以及其它的電路應用之中。

一個具有 q 電荷的粒子在磁場中移動時所承受的作用為  $F = qVxB \tag{3.3}$

上式中是對速度與磁場取向量乘積,因此作用力向量同時與速度向量及磁場向量相互垂直。

說明霍爾效應如圖 3-8。將一個具有 $I_x$ 電流的半導體置於一個與電流垂直的磁場之中。在這種狀況之中,磁場是在Z方向上。在半導體之中流動的電子與電洞將會感受到圖中所標示的力量。電子與電洞所承受的力量都是在(-y)方向上。在一個p型半導體 $[p_o>n_o]$ 之中,在半導體的y=0表面上則會有負電荷的堆砌。如同圖中所標示的,這個淨電荷會在y方向上感應一個電場。

圖 3-8 量測霍爾效應的幾何結構

在穩定狀態時,磁場的力量會剛好被感應電場的力量予 以平衡。這種平衡可以寫成

$$F = q[E+VxB]=0$$

(3.4a)

會成為

$$qE_y = qV_xB_z \tag{3.4b}$$

在 y 方向上的感應電場稱為霍爾電場(Hall field)。霍爾電場會產生一個跨越半導體的電壓,稱為霍爾電壓(Hall voltage)。我們可寫出

$$V_{\rm H} = +E_{\rm H}W \tag{3.5}$$

其中假設在+y方向上的 $E_H$ 是正的,而圖中所顯示的 $V_H$ 極性是正的。

圖 3-9 霍爾量測示意圖

在一個p型半導體中,電洞是多數的載子,因此圖中所定義的霍爾電壓是一個正的值。而在一個n型半導體之中的電子是多數載子,因此霍爾電壓會有相反的極性。霍爾電壓的極性可用以決定一個外質半導體是n型或p型。整理以上方程式可寫出

$$V_H = v_x W B_z \tag{3.6}$$

對一個 p 型的半導體而言,電洞的漂移速度可以表示為

$$v_{dx} = \frac{J_x}{ep} = \frac{I_x}{(ep)(Wd)}$$

(3.7)

其中e是電子的電荷量。再將上述兩式合併可得

$$V_H = \frac{I_x B_z}{epd} \tag{3.8}$$

或求解電洞的濃度,我們得到

$$p = \frac{I_x B_z}{e dV_H} \tag{3.9}$$

由電流、磁場、及霍爾電壓,我們可以決定多數載子的濃度。 對一個 n 型的半導體而言, 霍爾電壓是

$$V_H = -\frac{I_x B_z}{end} \tag{3.10}$$

因此電子的濃度為

$$n = -\frac{I_x B_z}{e dV_H} \tag{3.11}$$

注意在 n 型半導體之中的霍爾電壓是一個負值;因此,由方程式(3.11)所決定的電子濃度實際上是一個正的數量。一旦決定了多數載子的濃度,可以計算低電場時的多數載子的遷移率。對一個 p 型的半導體,我們可以寫出

$$J_x = ep\mu_p E_x \tag{3.12}$$

電流密度及電場可以被轉換為電流及電壓,因此上式會成為

$$\frac{I_x}{Wd} = \frac{ep\mu_p V_x}{L} \tag{3.13}$$

電洞的遷移率則是

$$\mu_p = \frac{I_x L}{epV_x Wd} \tag{3.14}$$

相類似地,對一個 n 型半導體而言,低電場的電子遷移率可由下式來決定

$$\mu_n = \frac{I_x L}{enV_x Wd} \tag{3.15}$$

- 圖 3-9 為霍爾量測的示意圖,當在霍爾量測時,為了取得 較精準的量測值,必須注意下列幾點:

- (1)量測時金屬與樣本連接必須在樣本邊界且完全密合。

- (2)樣本為同質性且厚度相同材料。

- (3)樣本表面為單一連接,不可有空洞或變形。

#### 3-4-2 量測之樣本介紹

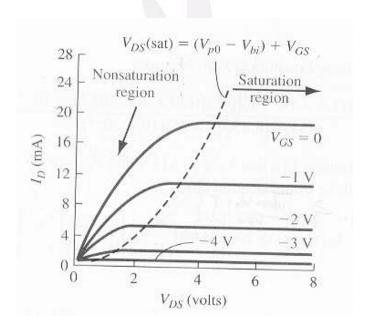

本次學生所做的 I-V 與高頻量測是以 MHEMT 結構中的 SGC-MHEMT 來分析。其中 MHEMT 有許多種類,在此學生以 PC-MHEMT 與 SGC-MHEMT 結構來做比較; PC-MHEMT 是基本 MHEMT 的形式其通道是以參雜固定的 InGaAs 為結構; 然而 SGC-MHEMT 是改變通道參雜的濃度,參雜濃度由低到高再降到低,使其通道能帶結構對稱,故我們稱為對稱式漸進式通道層電晶體。下表為 SGC-MHEMT 與 PC-HMET 結構比較表:

| Layers         | РС-МНЕМТ               | SGC-MHEMT            |  |

|----------------|------------------------|----------------------|--|

| Сар            | n+-In0.5Ga0.5As        |                      |  |

| Schottky       | i-In0.425Al0.575As     |                      |  |

| Carrier supply | δ-doped                |                      |  |

| Spacer         | i-In0.425Al0.575As     |                      |  |

| Channel        | i-InxGa1-xAs           | i-InxGa1-xAs         |  |

|                | x=0.65                 | $x=0.5\to0.65\to0.5$ |  |

| Barrier        | i-In0.425Al0.575As     |                      |  |

| Buffer         | i-InxGa1-xAs x=0 →0.45 |                      |  |

| Substrate      | S.I. GaAs Substrate    |                      |  |

由上表可知,兩者結構差異在於通道的參雜結構不同,其能帶圖的差異為圖

圖 3-10 PC-MHEMT 能帶圖

圖 3-11 SGC-MHEMT 能帶圖

因為 SGC-MHEMT 的通道參雜改變,能使載子侷限在較高銦成分之砷化銦鎵通道中央,因此可大幅提升元件直流、高頻特性,以獲得較優益之元件線性度、增加元件操作範圍。

## 3-4-3 元件的 I-V 量測

在先前章節 HEMT 結構介紹後,在本次專題中, SGC-MHEMT 結構來做高頻與 I-V 特性的分析。

對理想n通道的接面場效電晶體而言,洩極與源極的電 壓當

$$V_{DS} = V_{DS}(sat) = Vpo - (Vbi - Vgs)$$

(3.16)

洩極會被夾止,在飽和區域之中,我們可以藉由令方程式

$$I_{D1} = I_{p1} \left\{ 3(\frac{V_{DS}}{Vpo}) - 2\left[\frac{V_{DS} + Vbi - Vgs}{Vpo}\right]^{3/2} + 2\left(\frac{Vbi - Vgs}{Vpo}\right)^{3/2} \right\}$$

(3.17)

之中的 $V_{DS} = V_{DS}(sat)$ 來決定飽和洩極電流,因此

$$\boldsymbol{I}_{D} = \boldsymbol{I}_{D}(sat) = \boldsymbol{I}_{p} \left\{ 1 - 3\left(\frac{Vbi - Vgs}{Vpo}\right) \left[1 - \frac{2}{3}\sqrt{\frac{Vbi - Vgs}{Vpo}}\right] \right\}$$

(3.18)

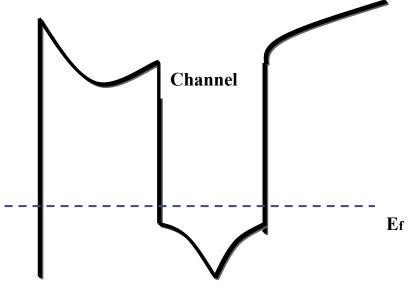

理想的飽和汲極電流與汲極-源極的電壓是無關的。圖 3-12 顯示一個 n 通道接面場效電晶體理想 I-V 特性。

圖 3-12 n 通道接面場效電晶體理想 I-V 特性

學生主要以量測 SGC-MHEMT 的特性為主,其結構圖為 下圖 3-13

圖 3-13 SGC-MHEMT 結構圖

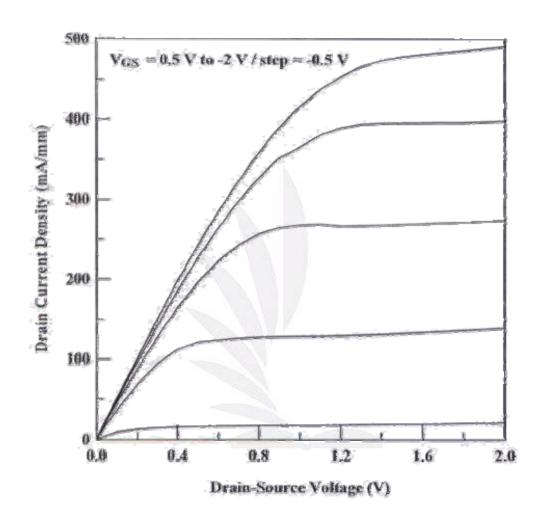

對於 SGC-MHEMT 我們量測出該該元件 I-V 特性圖(圖 3-14)

圖 3-14 SGC-MHEMT 的 I-V 特性圖

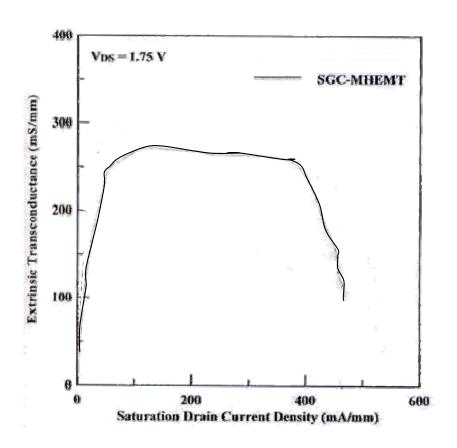

圖 3-15  $g_m$  VS.  $I_D(sat)$ 作圖,在  $V_{DS}$ =1.75V

由此圖我們可以觀測出該元件有很好的線性度,以及工作範圍很廣。

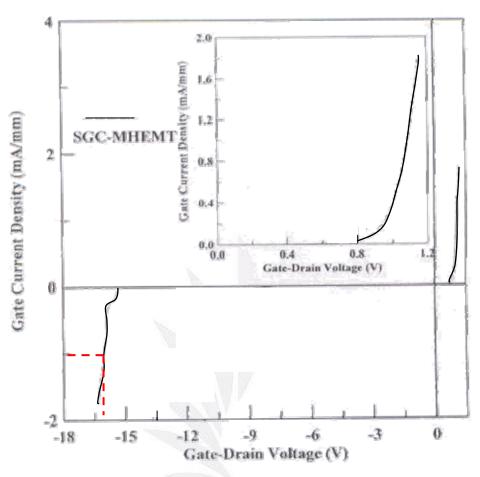

圖 3-16 閘極對汲極兩端點的崩潰電壓

定義當量測閘極電流密度為(-1mA/mm)時,為閘極崩潰電壓。由此可看出使用對稱式通道結構設計之 SGC-MHEMT能將載子侷限在通道中央,使得有效提高元件崩潰特性。

# 第四章 元件高頻參數萃取

近幾年無線通訊技術蓬勃發展,使得無線通訊積體電路逐漸取代個人電腦應用積體電路,成為驅動整個半導體技術的發展指標,尤其試射頻積體電路(RFIC)更是無線通訊應用中不可或缺的關鍵零組件。

由於各種無線通訊技術產品皆由各種主被動半導體元件及電路所構成。其中高頻半導體元件特性好壞與否,對於無線通訊產品的品質更扮演著舉足輕重的關鍵。為了提供高頻元件的製程及元件設計者更快速且詳實的元件特性,以作為進一步改良之依據;並且同時精準地提供電路設計者所需的資訊,高頻元件測試乃為一非常重要之關鍵技術,對於其相關之樑測技術及環境亦非常重視;以驗證其高頻元件及電路特性,確保其產品之品質及競爭力。

# 4-1 晶圓量測

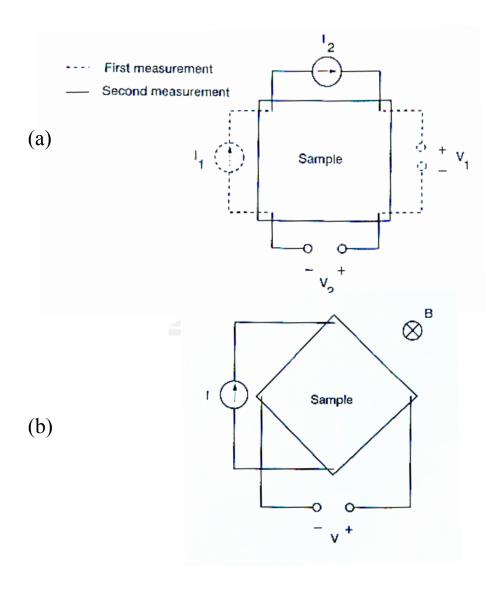

針對半導體元件進行高頻量測的方法可分為測試夾具法 (Test Fixture Measurement) 及 晶 圓 級 量 測 法 (On-wafer Measurement) 兩種, 兩種各有其優缺點。

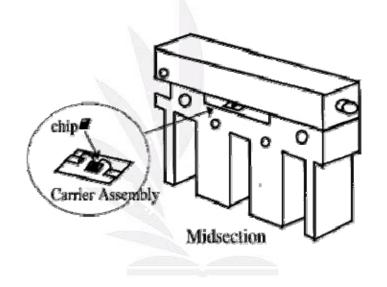

#### (1)測試夾具法:

此方法為較早其所發展的量測方式,該量測法可針對已 封裝或是尚未封裝的待測元件(Device Under Test, DUT)進行 量測。一開始必須把未包裝的晶片(Chip-Form)固定在載具 (Carrier Assembly)之上,並利用打線(Bonding Wire)連接元件 之金屬接觸點(Metal Pad)和載具上的微導線(Microstrip Line),然後將載具置於 Midsection 上,再把此 Midsection 夾 在已經做好校正的測試夾具上,如此即可進行測試夾具法的 量測,其關係圖 4-1。若為已包裝好的高頻元件則可直接將 該元件置於適當的 Midsection 上,再把此 Midsection 夾在已 經做好校正的測試夾具上後量測。經過元件切割且包裝後作 量測,能忠實地反映出元件包裝後的最終特性,如此便能提 供使用該元件的電路設計者元件包裝後最真實的元件特性資 訊。但由於必須把元件切割且包裝後才能進行量測,因此使 得元件封裝前的原始真實特性,因為封裝所需的打線及夾具 等的若干寄生效應而失真,如此一來,對於元件、製程設計 及改良之工程師而言,將無法真實地掌握元件原始特性,妨 害了元件製作上的改良及特性提升。量測未包裝的晶片雖可 免去前述之缺點,單所需的打線仍為一繁雜工作,且須另外 設計實驗方法或以數學運算去除所需打線的寄生效應。

圖 4-1 測試夾具法的量測

#### (2)晶圓級量測法:

為了克服測試夾具量測法的缺點,晶圓級量測法便應運而生,且已日漸成熟及普遍。此法主要是藉由共平面探針(Coplanar Probes)的使用來進行量測,此量測法可在元件製程

進行中段或是製程結束、封裝前使用,可藉由此方法得到元件封裝前的原始真實特性,避免封裝寄生效應的影響,有效地提高了元件特性及製程改良的可行性,同時也具有更高的時效性,並且節省封裝所需的成本。另外,與運用測試夾具的量測方式比較起來,其元件原始特性也較不易為其它寄生元件掩蓋,但其量測結果的重複性較易受操作人員之熟練度所影響。

# 4-2 參數量測與模型建立

原本在低頻時的雙阜網路是由 y, z, h 參數來表示,但 工作頻率超過 100MHz 線型的網路上, y、 z、 h 參數已不適 用,主要原因為,求這類的參數量測過程中,一定要將端點 作為斷路(open)或是短路(short)的處理,但是當頻率很高時, 電路的實際的斷路和短路很難段定。因此我們便使用 S 參數 來量測元件的高頻特性。

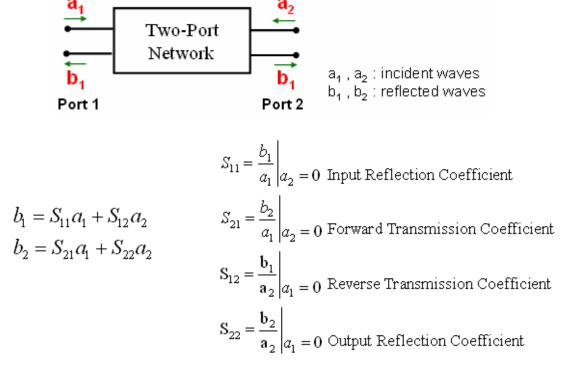

## 4-2-1 S 參數量測法

當電子電路操作在高頻的情況下時,該頻率所對應的波 長和實際電子電路的物理尺寸相較之下變小許多,因此,再 低頻時常用來描述電路節點特性的電壓和電流的觀念便逐漸 不適用,此時的電路特性用波或能量的觀念來表示將更為適 當,其中最常使用到的表示法為散射參數,又稱為 S 參數, 主要是採用入射波(incident)、穿透波(transmission)、和反射 波(reflection)的觀念來表示,利用入射波打到待測物的高頻微 波特性,如圖 4-2 所示。

圖 4-2 雙阜網路的 S 參數定義

量測 S 參數所需的系統架構,一般最為常見的頻率範圍可達 20 或 50GHz,此系統架構主要包含:

- (1) Network Analyzer:用來量測該雙阜網路(DUT)的 S 參數特性,並利用校正係數,將該量測系統的參考平面 移至靠近 DUT 處,以獲得並分析元件的高頻特性。

- (2) Synthesized Sweeper:用來提供射頻信號源。

- (3) Test Set:提供雙阜網路(Port-1 和 Port-2)快速切換能力,使得我們能夠很方便地測量對於描述雙阜網路所需之四個 S parameters。

- (4) DC Bias Supplies:用來提供待測元件的直流偏壓準位,並量測直流訊號響應。

在選擇了適當的量測方式,並完成校正程序之後,即將 待測元件接到 S 參數量測系統 50ohm 的雙阜之間。量測 S 參 數時。訊號由 DUT 的 Port-1 進入, Port-2 terminate, 此時所 量到的反射及傳輸功率比即分別為 S11 和 S21。藉由 Test Set 的切換功能,當訊號由 DUT 的 Port-2 進入, Port-1 terminate, 重複之前的量測,此時量到的反射及傳輸功率比,即分別為 S22 和 S12。藉由得到的 S11、S21、S22 和 S12 等四個 S 參 數特性,即可以得到元件的高頻特性並進一步的分析。

在分析微波電路時,場效電晶體的小訊號等效電路觀念 對於元件特性的分析相當有幫助。通常利用最佳化等效電路 中之元件參數值,使小訊號等效電路所表現出來的S值與實 際量測元件的S值相當接近。然而,目前此步驟仍存在如下 述之缺點:

- (1)需要準確量測的寬頻 S 參數裝置。

- (2)電路中的最佳元件值會隨著最佳化的方法與初始值而 有所改變。

- (3)使其具物理涵義,等效電路需要某些參數的預測值,如: 閘極電阻、電感。

為了克服這些困難,我們選擇晶圓高頻探測系統 (wafer-probing system)的方法,可快速且精確量測等效電路中本質與外質的元件值,以得到與電晶體製程相關參數,而且此參數萃取部分只需要網路分析儀(network analyzer)即可,亦為一極大優點。

# 4-2-2 模型參數萃取

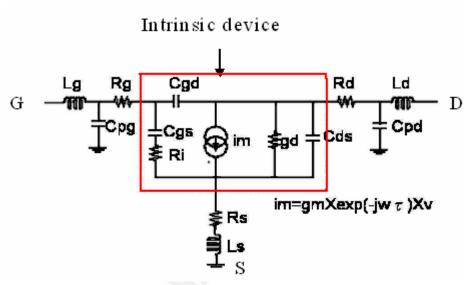

我們將小訊號等效電路分為有本質元件參數部分跟外質 元件參數部分,如圖 4-3。為了要得到各參數的數值,所以 我們將本質與外質分為兩個部分去求取。

圖 4-3 小訊號等效電路圖

### (1) 外質參數部分:

在外質參數部分,我們有寄生電感(L)、寄生電阻(R)、 寄生電容(C),其求取之偏壓點各有所不同。我們在每個頻率 點(0.1GHz~20GHz)都有對 S 參數進行量測,在此我們以 10GHz 為基準點。

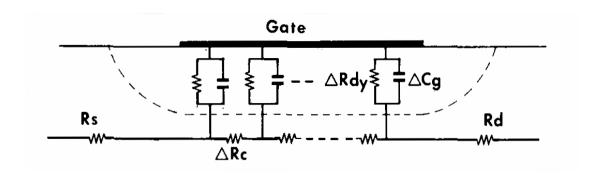

#### [1] 寄生電阻與寄生電感

在此我們先求取寄生電阻(R)與寄生電感(C),其偏壓點為Vds=0,Vgs>Vth,圖4-4為元件等效電分佈圖,整個電路的Z參數可以以下列式子表示:

$$Z11=Rc/3+Zdy (4.1)$$

$$Z12 = Z21 = Rc$$

(4.2)

$$Z22=Rc (4.3)$$

圖 4-4 順向偏壓下,元件等效電路分佈圖

其中 Rc 為通道電阻, Zdy 為蕭特基位障的等效阻抗, Zdy 可以表示如下:

$$z_{dy} = \frac{R_{dy}}{1 + jaC_g R_{dy}}$$

(4.4)

其中  $R_{dy} = \frac{nkT}{qI_g}$ , n 是理想因子,k 是波茲曼常數,Cg 是閘極電壓,Ig為閘極直流電流。所以閘極電流增加Rdy減少,Cg會增加。但因為Rdy隨Vgs以自然指數衰減,當閘極電流約為 $5\cdot 10^7$ - $10^8$ A/m²,6-4 式中的 $\omega\cdot$ Cg·Rdy趨近於零,4.4 式改寫成 4.5 式:

$$z_{dy} \cong R_{dy} = \frac{nkT}{qI_g}$$

$z_{dy} \cong R_{dy} = \frac{nkT}{qI_g}$  (4.5)

由於閘極電流很大,因此忽略閘極的電容效應,z11可以表示如式(4.6):

$$z_{11} = \frac{R_c}{3} + \frac{nkT}{qI_g} \tag{4.6}$$

另外把其餘外部寄生元件考慮進來其等效電路整體的 Z 參數表示如下:

$$Z11 = R_{s} + R_{g} + \frac{R_{c}}{3} + \frac{nkT}{qI_{g}} + j\omega(L_{s} + L_{g})$$

(4.7)

$$Z12 = Z21 = R_s + \frac{R_c}{2} + j\omega L_s \tag{4.8}$$

$$Z22 = R_s + R_d + R_c + j\omega(L_s + L_d)$$

(4.9)

將取得 S 參數的數值,使用 Microwave Office 這套軟體進行 S 參數轉 Z 參數的轉換,取得 Z 參數的實部數值跟虛部數值;將實部數值,另 Rc 與  $\frac{nkT}{qI_g}$ 為零,我們可以帶入上式  $(4.7 \cdot 4.8 \cdot 4.9)$ 求得寄生電阻  $(Rs \cdot Rd \cdot Rg)$ 。

在虚部數值部分,由於我們知道頻率與ω的關係式為

$$\omega = 2\pi f \tag{4.10}$$

將取得的 Z 參數虛部數值帶入式(4.7、4.8、4.9)之虛部部分,將可從

$$\begin{cases} Im(Z12)=Im(21)=\omega(Ls) & 求得 \ Ls \\ Im(Z11)=\omega(Lg+Ls) & 求得 \ Lg \\ Im(Z22)=\omega(Ls+Ld) & 求得 \ Ld \end{cases}$$

因此我們可以求得寄生電感(Ls, Lg, Ld)與寄生電阻 (Rs, Rg, Rd)。

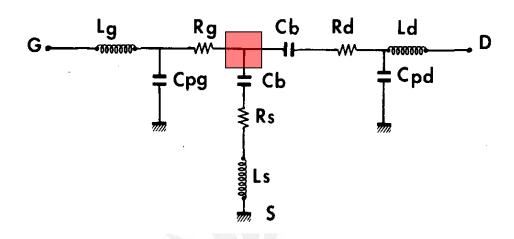

#### [2] 寄生電容

求取寄生電容(C)時,便設其量測偏壓點為 Vds=0V, Vgs < Vp(pinchoff),其此偏壓條件下的元件等效電路圖如圖 4-5;

圖 4-5 Vgs < Vp 元件等效電路分佈圖

其中 Cpg, Cpd, Cb 為外質寄生電容,當頻率到達數 GHz 時,電阻對Y參數的虛部沒有影響,如下列式子所示

$$\operatorname{Im}(y_{11}) = \omega(C_{pg} + 2C_b) \qquad \text{fig. Cpg} \qquad (4.11)$$

$$Im(y_{12}) = Im(y_{21}) = -\omega C_b$$

可求得 Cb (4.12)

$$\operatorname{Im}(y_{12}) = \operatorname{Im}(y_{21}) = -\omega C_b$$

可求得 Cb (4.12)  $\operatorname{Im}(y_{22}) = \omega (C_b + C_{pd})$  可求得 Cpd (4.13)

我們將該偏壓點所量測到的 S 參數轉成 Y 參數,並取出 虚部部分,將頻率帶入(4.10 式)求得ω,便可將所得的 Y 參 數虚部值帶入(4.11、4.12、4.13)三式,求取寄生電容(Cpg、 Cpd、Cb)。

藉由 Vds 固定為零,搭配 Vgs > Vth、 Vgs < Vp 作為兩種偏壓條件,萃取出所有的外部寄生元件參數(Ls、 Ld、 Lg、 Rs、 Rd、 Rg、 Cb、 Cpd、 Cpg),以下我們藉由外部寄生元件參數與 Microwave Office 軟體進一步萃取內部本質元件參數。

### (2) 本質參數部分:

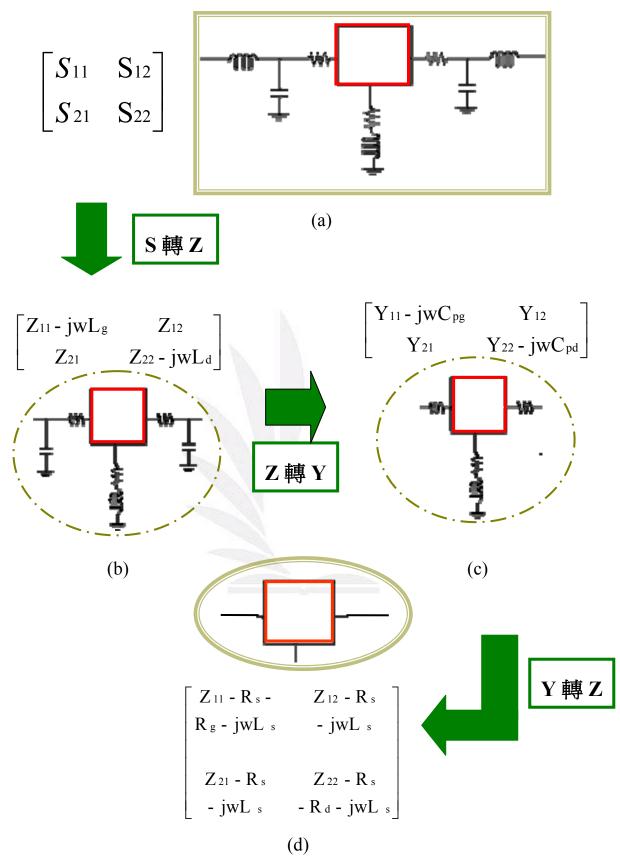

本質參數部分,我們有一個簡單的流程順序,圖 4-6,可以經由參數轉換,減去外質寄生元件的影響,進而利用雙阜網路的原理去推導本質部分的 Y 參數 ,並且求取出本質元件的數值,來建立元件小訊號參數的模型,進而比對實際量測的方法與模擬的結果,使其兩者相當接近。

圖 4-6 萃取本質參數流程圖

從圖 4-6 可知道我們從原先所量測到的 S 參數(a)圖,先轉成 Z 參數,在 Z 參數的矩陣內,我們可以將之前所求得的外質寄生電感(Lg,Ld)減去,(b)圖;再將減完寄生電感的 Z 參數轉換成 Y 參數,我們便可以利用 Y 參數的矩陣減去外質寄生電容(Cpg,Cpd),圖(c);將減完寄生電容的 Y 參數轉換成 Z 參數,在 Z 參數的矩陣內減去剩下的寄生電阻(Rs,Rd,Rg)跟寄生電感(Ls),圖(d);最後剩下本質參數元件,我再將 Z 參數轉換成 Y 參數,以便進而求出本質參數元件的數值,來求得元件完全的參數。

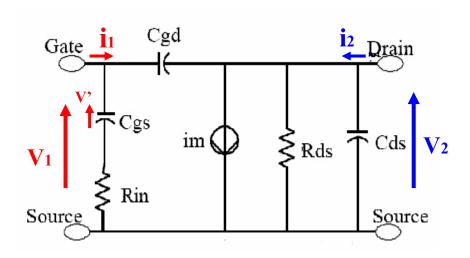

經過小訊號電路的外質寄生元件去除之後,我們只剩下本質元件,我們便開始進入求取本質元件的參數值,圖 4-7 為高電子遷移率電晶體(HEMT)的內部本質元件的小訊號等效電路,若在Gate與Source間加上輸入電壓時,Cgs兩端所跨的電壓V1'的im倍之電流會在Drain、Source間產生,把閘極電及下方的時間延遲考慮進去的話

$$i_m = g_m \cdot Exp(-j\omega\tau) \cdot V1'$$

(4.13)

τ表延遲時間。

圖 4-7 本質元件等效電路圖

我們利用雙埠網路理論去推導出本質部分的y參數

$$i_1 = y_{11}v_1 + y_{12}v_2 (4.14)$$

$$i_2 = y_{21}v_1 + y_{22}v_2 \tag{4.15}$$

$$y_{11} = \frac{i_1}{v_1}\Big|_{v_2=0}$$

$y_{12} = \frac{i_1}{v_2}\Big|_{v_1=0}$

$$y_{21} = \frac{i_2}{v_1}\Big|_{v_2=0}$$

$y_{21} = \frac{v_2}{i_1}\Big|_{v_1=0}$

推導出的 y 參數如式 4.16、4.17、4.18、4.19:

$$y_{11} = \frac{R_i C_{gs}^2 \omega^2}{D} + \left(\frac{C_{gs}}{D} + C_{gd}\right)$$

(4.16)

$$y_{12} = -j\omega C_{gd} \tag{4.17}$$

$$y_{21} = \frac{g_m \exp(-j\omega\tau)}{1 + jR_i C_{gg}\omega} - j\omega C_{gd}$$

(4.18)

$$y_{22} = g_d + j\omega(C_{ds} + C_{gd})$$

(4.19)

典型低雜訊元件,在頻率小於 5GHz 時,D 趨近於 1,則式 子化簡為:

$$y_{11} = R_i C_{gs}^2 \omega^2 + j\omega \left( C_{gs} + C_{gd} \right)$$

(4.20)

$$y_{12} = -j\omega C_{gd} \tag{4.21}$$

$$y_{12} = -j\omega C_{gd}$$

$$y_{21} = g_m - j\omega (C_{gd} + g_m (R_i C_{gs} + \tau))$$

(4.21)

$$(4.22)$$

$$y_{22} = g_d + j\omega(C_{ds} + C_{gd})$$

(4.24)

此時我們便將之前所求得的 Y 參數矩陣帶入(4.20,4.21, 4.22,4.23)之中,便可從實部,虛部去求得本質元件參數, ω=2πf 帶入下式

$$Re(Y11)=RiCgs^2\omega^2$$

可求得 Ri 可求得 gm 不e(Y21)=gm 可求得 gd 可求得 gd 可求得 Cgs  $Im(Y11)=\omega(Cgs+Cgd)$  可求得 Cgs  $Im(Y12)=-\omega Cgd$  可求得 Cgd  $Im(Y21)=-[Cgd+gm(RiCgs+\tau)]$  可求得 Cds 可求得 Cds

因此我們便求得全部的本質與外質元件參數值,進而建立 小訊號等效電路模型。

## 4-2-3 元件模擬與結果分析

在此我們以 MHEMT 為實際量測的元件並進行參數萃取,求得小訊號模型元件的參數。我們將量測頻率從0.1GHz到20GHz,並且取10GHz為基轉點進行元件參數萃取。

由上述的 Cold Model 的量測理論、與矩陣運算等方法, 成功萃取出 HEMT 的元件參數:

- (1) 外質寄生元件參數(Ls, Ld, Lg, Rs, Rg, Rd, Cpg, Cpd)

- (2) 本質元件參數(Cgs, Cgd, gm, gd, Ri, τ)

將這些參數代入高電子遷移率電晶體的微波模型透過 Microwave Office軟體進行模擬,再與實際量測的數值比對、 然後透過軟體將參數再微調,使實際量測與模擬結果比對差 異最小化,以建立完整而準確的微波模型。 我們將元件參數萃取分為三個偏壓點去進行 S 參數對頻 率的量測,各個偏壓點有其萃取出的元件參數值。

- (1) 外質寄生電阻與寄生電感: Vds=0V, Vgs=1V

- (2) 外質寄生電容: Vds=0, Vgs=-3V

- (3) 本質元件參數萃取: Vds=2V, Vgs=-1.5V

## (1) 外質寄生電感與寄生電阻參數萃取值:

偏壓點 Vds=0V, Vgs=1V; 結果如表 4-1

|      | Rs (ohm) | 0.07421   |

|------|----------|-----------|

| 寄生電阻 | Rg (ohm) | 0.48754   |

|      | Rd (ohm) | 0.13893   |

| 寄生電感 | Ls (nH)  | 0         |

|      | Lg (nH)  | 0         |

|      | Ld (nH)  | 0.0005802 |

表 4-1 外質寄生電阻與電感萃取參數表

## (2) 外質寄生電容參數萃取值:

偏壓點 Vds=0V, Vgs=-3V; 結果如表 4-2

| 寄生電容 | Cpg (pF) | 0.12678 |

|------|----------|---------|

|      | Cpd (pF) | 2.3322  |

|      | Cb (pF)  | 1.46965 |

表 4-2 外質寄生電容萃取參數表

# (3) 本質元件參數萃取值:

偏壓點 Vds=2V, Vgs=-1.5V; 結果如表 4-3

|      |      | Cgs (pF) | 11.027        |

|------|------|----------|---------------|

|      | 電容   | Cgd (pF) | 0.5255        |

|      | ,    | Cds (pF) | 0             |

| 本質元件 | 轉導   | gm (mS)  | 4313.4        |

| 參數   |      | gd (mS)  | 142.245       |

|      | 電阻   | Ri (ohm) | 0             |

|      | 延遲時間 | τ (pS)   | 0.00080297766 |

表 4-3 本質元件參數表

從上表我們成功的萃取出元件的參數值,我們便可以將這些元件參數帶入高電子遷移率電晶體透的微波模型透過Microwave Office 這套軟體進行模擬。

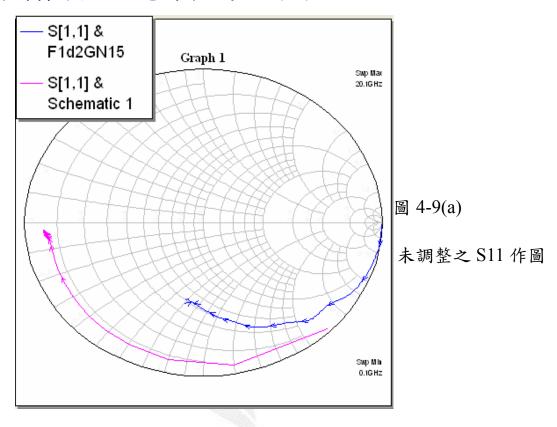

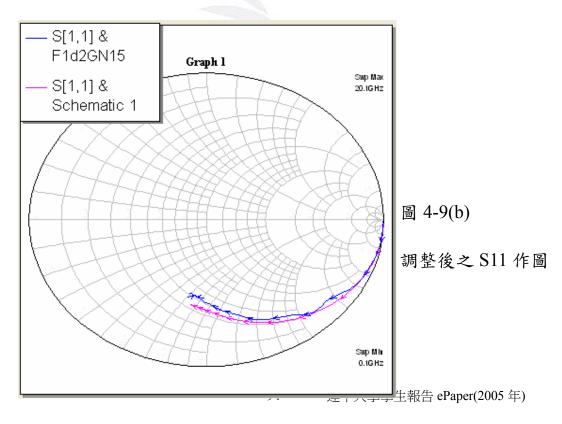

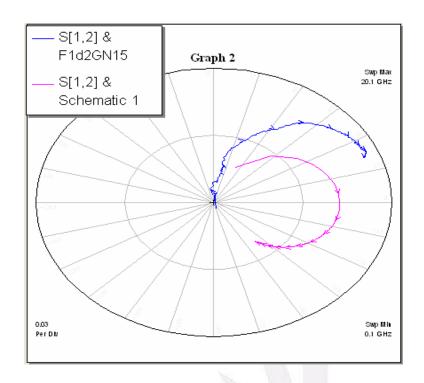

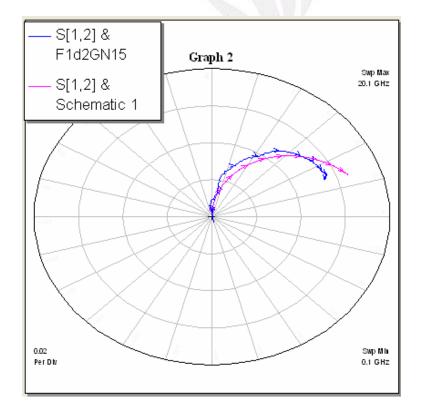

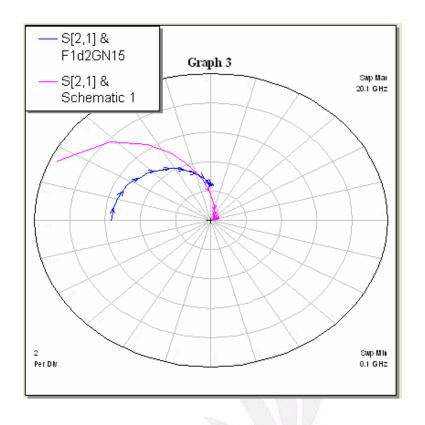

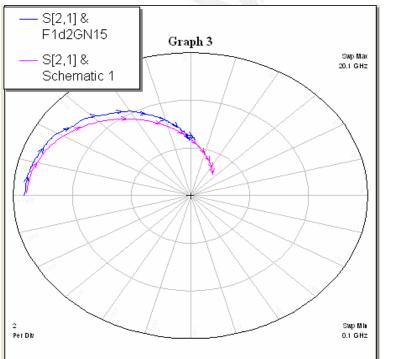

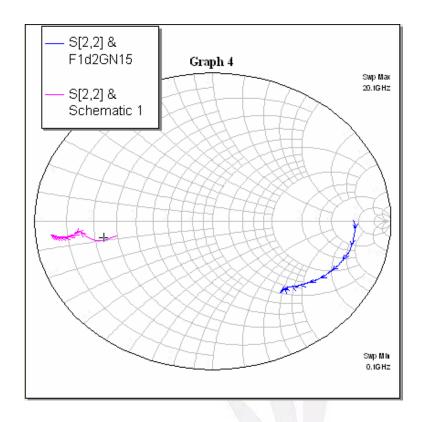

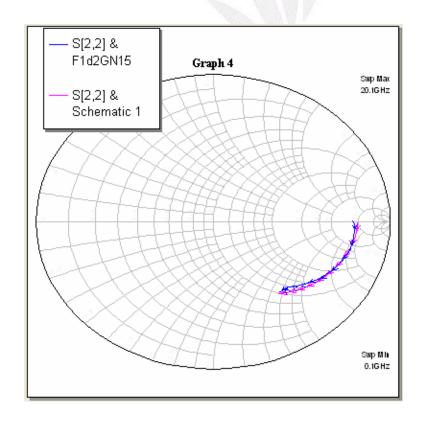

將我們原本實際值所量測的元件 S 參數畫為 Smith chart 圖,並與我們所萃取出的元件參數值帶入微波模型畫出的 Smith chart 圖比較,再將我們模擬出的圖進行元件參數的調變,使模擬的圖近似量測實際值的圖。

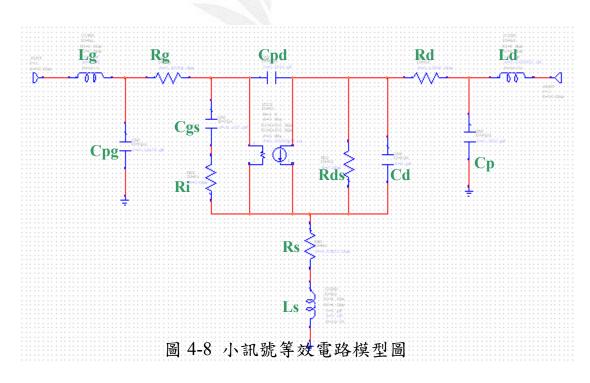

我們先接妥電路並且輸入我們所計算出的元件初始值, 然後先畫出未調變過比較圖。圖 4-8 是我們所接好的小訊號 等效電路模型。

下圖 4-9、4-10、4-11、4-12 是我們所萃取出的元件參數

作圖(未經調整)與量測的原始圖與調整後的圖作比較。 我們要將兩條縣調整到相近便可以獲得最正確的元件參數值;藍線為實際值,紅色為萃取參數作圖。

圖 4-10(a) 未調整之 S12 作圖

圖 4-10(b) 調整後之 S12 作圖

圖 4-11(a) 未調整之 S21 作圖

圖 4-11(b) 調整後之 S21 作圖

圖 4-12(a)

未調整之 S22 作圖

圖 4-12(b)

調整後之 S22 作圖

由此方法我們便可以獲得元件的小訊號等效電路模型內的各個參數值。

| 外質元件參數   |           |  |  |

|----------|-----------|--|--|

| Lg (nH)  | 0         |  |  |

| Ls (nH)  | 0         |  |  |

| Ld (nH)  | 0.016043  |  |  |

| Rs (ohm) | 4.7135    |  |  |

| Rg (ohm) | 22.796    |  |  |

| Rd (ohm) | 14.084    |  |  |

| Cpd (pF) | 0.0039907 |  |  |

| Cpg (pF) | 0.053918  |  |  |

| 本質元件參數   |           |  |  |

| Cgs (pF) | 0.010208  |  |  |

| Cgd (pF) | 0.0095614 |  |  |

| gm (mS)  | 8.4       |  |  |

| gd (mS)  | 0.1598    |  |  |

| Ri (ohm) | 30.49     |  |  |

| T (pS)   | 0.004023  |  |  |

# 第五章 結論

經由研究高電子遷移率電晶體(HEMT)讓我了解到該元件的材料選擇、演進歷程、元件特性與結構設計:

- (1) 傳統通道由 Undoped 的 GaAs 演進到較快速的 InGaAs 通 道層,因為通道參雜銦(In)元素的關係,使得電子傳輸速 率便快。

- (2) 因為異質結構的關係,使得導電帶不連續形成一個量子井,因此載子侷限在此量子井內形成二維電子雲,載子因此只有在二維空間內傳動,所以 HEMT 才有很高速的電子遷移率。

- (3) HEMT 的發展演進

- [1] 傳統的 AlGaAs/GaAs 異質結構電晶體

- [2] 因為傳統的異質接面電晶體 μ 不夠高、載子侷限能力不夠強,所以將通道層改變為 InGaAs 因為銦(In)的參雜可以使的 μ 提升,效能變好;由於 InGaAs 與 GaAs 晶格常數不匹配所以我們不能把 In 參雜太

- 高,因此該通道層做的很薄使得 InGaAs 與 GaAs 兩者的晶格排列看起來類似,稱為假晶式通道電晶體(PHEMT)。

- [3] 接著演變成以 InP 為基板 InP/InGaAs 異質結構的電晶體(InP HEMT),因為 InP 為基板所以通道 In 的參雜濃度增加,使得電子遷移率(µ)會隨著便快。

- [4]由於 InP 基板的成本高易碎,又演進成現今已 GaAs 為基板的調變式緩衝層結構的(MHEMT),由於 GaAs 基板與 InGaAs 基格不匹配,所以我們將緩衝層作為 InAlAs 並且將 In 的參雜濃度由低往高參雜,使得通道層的 InGaAs 的 In 濃度可以參雜高一點,所以稱為 MHEMT。

- (4) 結構的設計上我們可以將 HMET 作為多通道、單通道或 是使通道曾為參雜而多做一層載子提供層(δ-doped)等設 計。

並且實務該元件之製程,半導體特性量測,S參數萃取以及一連串富含物理意義之矩陣運算後,配合 HEMT 高頻模型之電路模擬參數值最佳化,預期實驗與模擬結果比對可得兩者數據差異極小,建立完整 HEMT 高頻小訊號等效電路。無線通訊中,射頻積體電路(RFIC)設計為非常重要的一環,因此提供完整並準確的元件高頻模型成為 IC 設計能否符合預期效能及規格的關鍵。本專題配合學生之前所修習的半導體元件及 IC 製程課程,利用電腦模擬工具(Microwave Office)將元件電路參數最佳化,不僅可讓學生更加熟悉目前業界所使用之半導體元件之特性及製造之流程,進而加以設計調變元件及製程參數,以獲得最佳化的結果。

本專題製作過程中,讓我們對化合物半導體元件有更多的認識與學習並用實驗量測來驗證結果。製作專題時,曾數次到成大實驗室學習製程與量測技巧,使得我們往後的研究奠定紮實的基礎。感謝指導老師 李景松老師的教導與實驗室的學長們的指導與照顧,我將以主動積極、努力認真且謙虛之學習態度,凡是盡心盡力、全力以赴的研究精神來面對任何研究領域,並將專題中所學,應用在日後的研究上。

### 【參考資料】

- [1] 本城和彥 著,呂學士 編譯,"微波通訊半導體電路", 全華科技圖書,民國85年3月。

- [2] 施敏 原著, 黃調元 譯, "半導體元件物理與製作技術", 國立交通大學出版社, 2002年9月。

- [3] S. M. Sze, "Physics of Semiconductor Devices," Johy Wiley &Sons, 2<sup>nd</sup> Edition, 1981.

- [4] S. M. Sze, "High-Speed Semiconductor Devices," Johy Wiley &Sons, 1990.

- [5] Donald A. Neamen, "Semiconductor Physics and Devices", 3<sup>rd</sup> ed.,McGraw-Hill,New York,2003.

- [6] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit," IEEE Trans. Microwace Theory Tech., vol. 36, pp. 1151-1159, July 1988.

- [7] H. Fukui, "Determination of the basic device parameters of a GaAs MESFET," Bell Syst. Tech. J., vol. 58, no. 3, pp. 771-795, 1979.

- [8] W. R. Curtice and R. L. Camisa, "Self-consistent GaAs FET models for amplifier design and device diagnostics," ZEEE Trans. Microwave Theory Tech., vol. MTT-32, pp. 1573-1578, Dec. 1984.

- [9] Loi D. Nguyen et al., "Influence of quantum-well width on device performance of Al,,,,Ga,,,,As/In,~,,Ga,,,,As (on GaAs) MODFET's," IEEE Trans. Electron Deuices, vol. 36, pp. 833-838, May 1989.

- [10] F. Diamant and M. Laviron, "Measurement of the extrinsic series elements of a microwave MESFET under zero current condition," in Proc. 12th European Microwave Conf., 1982, pp. 451-456.

- [11] W. R. Curtice and R. L. Camisa, "Self-consistent GaAs FET models for amplifier design and device diagnostics," IEEE Trans. Microwme Theory Tech., vol. MTT-32, pp. 1573-1578, Dec. 1984.

- [12] R. A. Minasian, "Simplified GaAs MESFET model to 10 GHz," Electron. Lett., vol. 13, no. 8, pp. 549-541, 1977.

- [13] K. W. Lee, K. Lee, M. S. Shur, Tho T. Vu, P. C. T. Roberts, and M. J. Helix, "Source, drain and gate series resistances and electron saturation velocity in ion implanted GaAs FET's," IEEE Trans. Electron Devices, vol. ED-32, pp. 987-992, May 1985.

- [14] P. L. Hower and N. G. Bechtel, "Current saturation transistors," IEEE Truns. Electron Devices, vol. ED-20, pp. 213-220, Mar. 1973.

- [15] A. Cappy, "Propriitks physiques et performances potentielles des composants submicroniques a effet de champ: Structure conventionnelleet & gaz d'ilectron bidimensionnel," These de Doctorat, Lille, France, 1986.