### 逢甲大學學生報告 ePaper

#### 報告題名:

### 藉由不同堆疊結構對提升鍺/矽p+n二極體分析

作者:游承儒 王仁佑 陳俊嘉

系級:電子四甲 電子四乙

學號: D9323650 D9366188 D9366751

開課老師:李景松

課程名稱:化合物半導體元件

開課系所:電子四甲

開課學年: 九十六 學年度 第 一 學期

藉由不同堆疊結構對提升鍺/矽p+n 二極體量測與分析

中文摘要

本專題的研究中,主要是探討提升源極/汲極(Raised Germanium

Source/Drain )結構實驗的結果。發現提升鍺二極體的漏電流極大,這

是由於接面空乏區有差排的分布,其逆偏1V的面積漏電流密度為

1.35E-3 A/cm<sup>2</sup>。所以在堆疊鍺之前,先沉機一層矽化鍺,使晶格差異

變小,可以大幅的降低漏電流。

另一方面,利用超高真空化學氣相沈積系統(Ultra High Vacuum

Chemical Vapor Deposition System, UHVCVD System )做一般的沈

積,因製程時間過長造成硼往矽基板方向擴散至較深的接面深度,利

用不同堆疊(Stack)結構可以使接面深度大幅地改善,但漏電流只有

些微提高。

關鍵字: 鍺、提升源極/汲極

逢甲大學學生報告 ePaper(2007年)

#### 目 次

| 摘要                                         | 1     |

|--------------------------------------------|-------|

| 目錄                                         | 2     |

| 圖目錄                                        | 4     |

| 第一章緒論                                      | 5     |

| 1.1背景介紹                                    | 5     |

| 1.1.1提升源極/汲極(Raised Source/Drain)結構與選擇     | 性磊晶成長 |

| (Selective Epitaxial Growth, SEG)技術        | 5     |

| 1.1.2金屬矽化物(Silicide)製程技術的發展                | 8     |

| 1.1.3 應變矽(Strain Silicon)技術                | 10    |

| 1.2 量測方法                                   | 15    |

| 1.2.1 漏電流量測                                | 15    |

| 1.2.2 SIMS量測                               | 17    |

| 1.3專題研究動機                                  | 19    |

| 1.4本專題之內容                                  | 20    |

| 第二章 元件製作                                   | 21    |

| 2.1 晶片刻號及零層蝕刻                              | 21    |

| 2.2 形成Field Oxide ( LOCOS Process)         | 22    |

| 2.3 選擇性磊晶成長( Selective Epitaxial Growth )鍺 | 22    |

| 2.4覆蓋保護層( Passivation Layer )與活化( Activation )    | 23     |

|---------------------------------------------------|--------|

| 2.5 做間隙壁(Spacer)以及金屬矽化物(Silicide)製程               | 24     |

| 第三章 不同堆疊結構對提升鍺/矽p <sup>+</sup> -n二極體特性之影響         | 29     |

| 3.1 簡介                                            | 29     |

| 3.2 量測設計                                          | 30     |

| 3.2.1漏電流                                          | 30     |

| 3.2.2 SIMS 量測 ··································· | 30     |

| 3. 3結果與討論                                         | 31     |

| 3.3.1 漏電流分析                                       | 31     |

| 3.3.2 SIMS 分析                                     | 32     |

| 3.4 結論                                            | 34     |

| 第四章 總結                                            | ····45 |

| 參考文獻                                              | ··· 46 |

# 圖目錄

| 圖2.1 元件LOCOS的形成                       | 25 |

|---------------------------------------|----|

| 圖2.2選擇性磊晶並以臨場摻雜示意圖                    | 26 |

| 圖2.3覆蓋一層TEOS作為保護層示意圖                  | 27 |

| 圖 2.4 乾式蝕刻製作間隙壁圖                      | 28 |

| 圖2.5 製作Silicide圖                      | 28 |

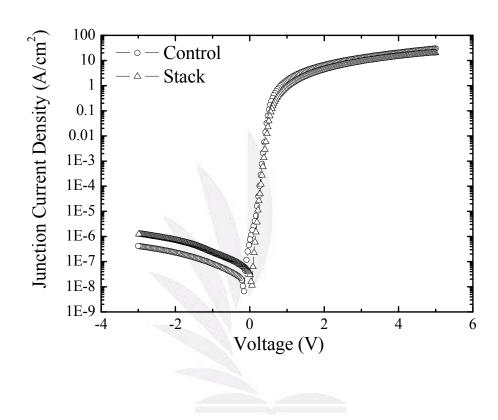

| 圖3.1 不同堆疊結構之I-V比較                     | 35 |

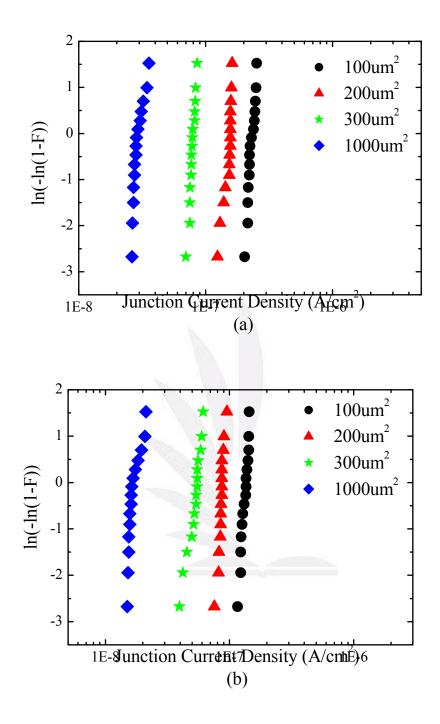

| 圖3.2 不同堆疊條件在-1V的漏電流機率分佈圖              | 36 |

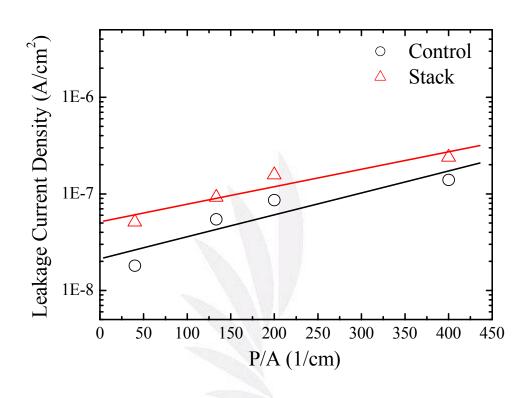

| 圖3.3 不同堆疊條件在-1V的漏電流密度對周長面積比圖          | 37 |

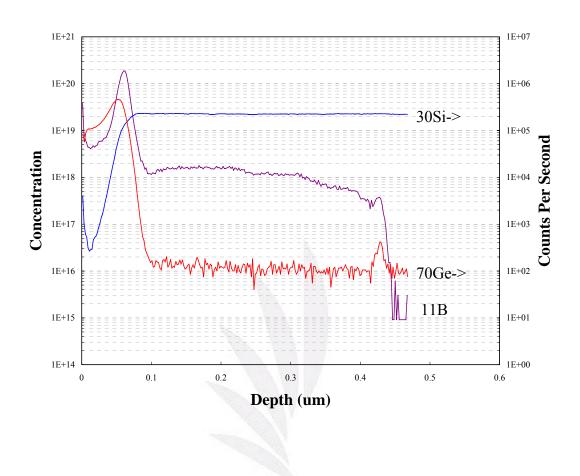

| 圖3.4 真空環境下做活化的Control Sample的SIMS圖    | 38 |

| 圖3.5 真空環境下做活化的Control Sample的SIMS圖    | 39 |

| 圖3.6 通N2O環境下做活化的Control Sample的SIMS圖  | 40 |

| 圖3.7 通N2O環境下做活化的Control Sample的SIMS圖  | 41 |

| 圖3.8真空環境下做活化的Stack Sample的SIMS圖       | 42 |

| 圖3.9真空環境下做活化的Stack Sample的SIMS圖       | 43 |

| 表目錄                                   |    |

| 表3.1 Control sample和Stack sample的理想因子 | 44 |

# 第一章 緒論

#### 1.1 背景介紹

# 1.1.1 提升源極/汲極(Raised Source/Drain, RSD)結構與選擇性磊晶成長(Selective Epitaxial Growth, SEG)技術

在先進的極大型積體電路(ULSI)的發展上,必須應用到源/ 汲的超淺接面技術(Ultra-shallow junction),來消除熱電子注入 (hot carrier injection)及短通道效應(short channel effect)的影響。因此,如何積極有效的縮減接面深度,維持摻雜載子濃度 所需努力的方向。目前有許多方法被用來形成超淺接面,包括分子 來雷射摻雜、侵入式氣體雷射摻雜、磊晶摻雜及低能量離子佈植 [1]-[4]。離子佈植是目前最為廣泛應用的超淺接面形成技術,由於它 具有精確的可控制性、均勻性及重覆性。實際上,p<sup>+</sup>-n超淺接面的形 成要比n<sup>+</sup>-p超淺接面的形成來的困難,因為硼(B)原子的質量很輕, 導致雜質產生相當大的擴散範圍和穿隧效應。

利用低能量硼離子佈植到矽基版,會產生較深的接面深度和穿隧效應。有許多方法被用來減少隧道效應的發生,其中將矽基版抬高7°[5],可有效降低穿隧效應。雖然這種技術可以成功地應用在典型的

離子佈植中,但在低能量離子佈植中,隧道效應會隨著能量減少而更嚴重。在非常低的能量中,使用更大的角度是必須的,但整體效益卻變的更有限。大量的偏移及旋轉角度會產生兩個缺點,(1)濺鍍表面原子的機率增加,導致矽表面粗糙度增加,及先前植入的雜質被去除;(2)做光罩時,會有陰影效應的產生。鍺與矽的預先非晶化佈植,或以犧牲氧化層為阻擋,減少硼離子隧道效應發生的方法,已被發展使用[6]-[7]。但大部份的雜質將會遺失在這非晶層中,而導致片阻值上升。況且,非晶化在一定的條件下,會增強硼離子的擴散。例如,在非常低的佈植能量及高溫熱退火下,經過非晶化的接面將比沒有非晶化的接面更深[8]。

當 MOSFETs 持續縮小到 0.1µm 以下,需要極淺接面用來抑制短通道效應(Short Channel Effect, SCE),不過減少接面深度會造成較大的源極/汲極寄生電阻。為了解決此問題,提高源極/汲極(Raised source/drain, RSD)結構已經被發展出來。一般 RSD 結構不適合用於超接面的形成是由於摻雜 RSD 層需要相當高能量的離子佈植,此方法會使得摻雜離子可能穿透 RSD 層,造成超淺接面的失敗,因此後來發展出了摻雜選擇性磊晶成長(In-situ Doped Selective Epitaxial Growth, In-situ Doped SEG)技術[9]。

矽的臨場摻雜選擇性磊晶成長(Selective Epitaxial Growth, SEG)

技術已經被用於製造含有提高源極/汲極的 CMOS 元件。含有 RSD 結 構的元件能夠有效地降低熱載子在一般元件上的影響,為了限制在深 次微米 MOSFETs 的熱載子的數量,縮小通道內的汲極側壁電場是必 須的。為了達到這個目的,輕摻雜汲極( Light Doped Drain, LDD )結 構被應用於此,不過,深次微米 MOSFETs 限制了 LDD 技術的應用, 因為 LDD 技術會增加整體元件的尺寸[10]。以矽化物作為雜質擴散源 (Silicide as Diffusion Source, SADS)的製程,已經被證實可作為接面 深度低於 0.1µm 的選擇[11] - [13]。在這個製程中, 雜質被植入矽化物 及後續的熱處理,將使得雜質擴散進入矽基版而形成超淺接面。此接 面完全不會受到離子佈植所造成的傷害,因為雜質完全被限制在矽化 物的範圍內。因此利用低熱預算製程,即可形成低漏電流且高品質的 接面。而臨場摻雜選擇性磊晶成長(In-situ Doped SEG)技術與SADS 的效果相同,同樣具有形成超淺接面的能力,因此成為成為形成超淺 接面的主要技術之一。

對於深次微米的互補式金氧半導體(CMOS)元件來說,要維持元件高速操作的特性,降低寄生電阻是一個重要的關鍵。自我對準矽化物(Salicide)製程,已廣泛地應用在CMOS的製程當中,用來降低淺接面和複晶矽閘極的片電阻以及增加源極/汲極接面的接觸區。然而,超淺接面的矽化反應過程,會導致較大的漏電流,這是由於在矽

化反應過程後,接面深度將變的更淺。 一般超淺接面的矽化反應過程會造成較大的漏電流,並且增加製作超淺接面的困難度,進而使用了 RSD 結構來改善此缺點。

使用提高源極/汲極(Raised Source/Drain, RSD)結構作為CMOS 元件的製程之一,由於此結構使用臨場摻雜選擇性磊晶成長(In-situ Doped SEG)技術,故能有效地形成超淺接面;而進行自我對準金屬 矽化物(Salicide)技術時,由於金屬是與RSD結構的矽產生反應,而 非矽基版的矽,因此能夠避免超淺接面被矽化反應破壞。

#### 1.1.2 金屬矽化物(Silicide)製程技術的發展

由於電阻和傳導線的截面積成反比,因此當元件縮小後,寄生電阻會顯著上揚(假設厚度不變),這對於奈米元件的操作影響很大。 金屬砂化物具有高熔點、高穩定性及低電阻率等優點,於積體電路製程上的應用已經是必要的製程技術之一[14]。目前被廣泛應用於積體電路的製程中解決寄生電阻問題的方法為「自動對準」的金屬矽化物(Self-Aligned silicide,簡稱Salicide)[15-17]。 採用「自動對準」的金屬矽化物除了可降低接面接觸電阻、閘極電阻,進而提高整個元件的驅動電流,反應時間或電路的操作速度外,在金屬矽化物製程上,有一個特點,即自動對準功能。 早期的金屬矽化物材料是矽化鈦,然而隨著元件尺寸的日益縮小,矽化鈦之製程面臨極大的挑戰。 因

為矽化鈦在矽化過程中,會產生橋接短路效應 (Bridge Short Effect) [18],而且當複晶矽線寬小於 0.5 µm或高摻雜砷濃度時,鈦矽化物無 法由高阻值的C49 相位(晶粒尺寸小至 0.1-0.2 μm)轉換成低阻值的 C54 相位 (1-10 μm巨大晶粒) [19-22]。 另外, 鈦與閘極摻雜物易形 成穩定鍵結(如TiB2),造成接面濃度下降,而影響接觸特性,因此 上述的缺點造成在元件尺寸縮小之際,TiSio於閘電極上的應用變得不 適用。 而矽化鈷正好可以彌補矽化鈦的種種缺點,在自行對準方面, 由於鈷在形成矽化鈷時是擴散源,所以並沒有像矽化鈦在矽化反應時 的橋接短路效應,種種的優點都使得矽化鈦漸漸被矽化鈷所取代。但 以鈷當做金屬矽化物的材料也並非全無缺點,例如鈷金屬與矽原子在 進行矽化反應時,會消耗大量的矽(1:3.2),所以對於超淺接面元件 所使用的鈷金屬厚度就必須減少,而且在進行矽化反應時,其對自生 氧化層 (Native Oxide) 的存在極為敏感。 並且使用矽化鈷作為金屬 接觸的最大問題,在於矽化鈷形成的時候,矽化鈷與矽基板 (Si Substrate )的界面並不是平整的,且會有熱凹槽( Thermal Grooving ) 的現象產生,造成矽化鈷薄膜的結塊 (Agglomeration),降低矽化鈷 超淺接面的熱穩定性[23]。另一個應用在積體電路上的當做金屬矽化 物為矽化鎳(NiSi),常它基本上和CoSi<sub>2</sub>相似,同樣沒有TiSi<sub>2</sub>種種 的缺點,但NiSi還有很多特性優於CoSio且適合應用於奈米尺寸的

CMOS製程上[24-25]。 例如: (1)NiSi矽化物可以在 400℃到 600℃的 低温下形成,而且擁有相當寬的製程溫度窗口,(2)NiSi在微小線寬下可被輕易形成,不會有相位轉換的問題[26-29],(3)NiSi矽化物形成過程所消耗的矽較TiSi₂和CoSi₂小,(4)NiSi的薄膜應力也較TiSi₂和CoSi₂ 低很多,(5)NiSi的矽化過程傾向於金屬移動到矽基座或複晶矽薄膜與矽反應,因此它幾乎沒有Creep-up現象,(6)與TiSi₂比較,NiSi在掺雜方面也有較佳的穩定性,於是目前最受矚目的便是矽化鎳(NiSi)之研發與應用。

#### 1.1.3 應變矽(Strain Silicon)技術

在過去 30 年間, MOSFET 的間極線寬已從 10μm 縮減到 45 nm。由於在製造 CMOS 的技術上,可以使功率消耗不斷降低,因此造就了 CMOS 元件成為 IC 工業中最佔優勢的技術。而最令人驚異的是, MOSFET 的結構在這 30 年間僅改變少許。 在這 30 年間, Intel 邏輯工業中, MOSFET 結構的革命性改變,主要的結構改變有如[30],(1)在 1970年,使用鋁金屬(Al)於複晶矽閘極。 (2)在 1980年,側壁(Spacer)的增加、低掺雜汲極(Light Doped Drain, LDD)以及自行對準矽化物。 (3)2003年矽化鎮金屬材料(NiSi)與受機械應力的應變矽於90 nm 技術中產生,受機械應力的應變矽目前依舊受到矚目並持續發

展中。

由於矽的晶格常數 (Lattice Constant)為 5.43 Å, 鍺則為 5.65 Å, 兩者相差約4%, 因為鍺晶層之晶格(Lattice)常數較矽晶體長約 4%,所以矽鍺層需有所形變(Strain),使其在平面(In-plane)方向的 晶格常數縮小以與矽層相同,在成長縱向(Out-of-plane)方向則增加。 此種結構的形變的型式稱為壓縮形變(Compressive Strain)。 另外一 種主要的磊晶結構是將晶格常數較小的薄矽層成長在晶格常數較大 的矽鍺層上,使其在平面方向的晶格增長以與矽鍺層相同,在縱向方 向則縮小。此種結構的形變的型式稱為擴張形變(Tensile Strain)。此 種結構係以矽基板為主體,先行成長一矽鍺緩衝層(Buffer Layer), 一般矽鍺緩衝層的厚度為數微米,其中的鍺含量以漸進的方式增加, 以將形變能量控制在矽基板處釋放,並將產生的差排等缺陷侷限在基 板內。 能量釋放後的緩衝層最表面晶格常數回復無形變(Relaxed) 時的狀態,但保持低缺陷密度。 之後在於其上成長擴張形變的薄矽 層。 此種結構由於能同時增進電子與電洞的遷移率(Mobility),提升 元件的驅動電流,因此適合互補式金氧半場效電晶體(CMOS)元件的 研製。 這種能夠同時改良 PMOS 與 NMOS 的特性元件,一般稱為應 變矽通道 COMS 元件。 實驗上已驗證應變矽通道無論是使用在 PMOS 或 NMOS,均能顯著地增進驅動電流,加快電路的操作速度

[31]。 這則歸因於應變矽通道中的形變引起的導帶(Conduction Band) 與價帶(Valence Band)的分離(Splitting),能減少電子的谷間散射 (Inter-valley Scattering)與電洞的能帶間散射(Inter-band Scattering),同時也減少載子的等效質量(Effective Mass),所以遷移 率獲得了有效地提昇。

應變矽通道COMS由於能增進元件與電路的效能,因此深受業 界的矚目。但是在實際應用之時,仍須對可能產生的問題進一步地 掌控[32]。 像是:(1)基板缺陷。 一般使用矽鍺緩衝層的缺陷密度 在 103~104 cm-2的範圍,必須要確定這些缺陷不會影響晶片內千萬個 元件的遷移率( Mobility )及接面漏電流。 (2)表面平坦度。 矽鍺緩 衝層磊晶成長後,表面會較原來的晶圓面粗糙,並因而造成後續成 長閘氣層的漏電流增加與可靠度劣化。 一般可以藉由化學機械拋光 研磨(CMP)處理來改善[33]。 (3) n型元素的擴散。 n型元素,如磷 與砷,在矽鍺內的擴散速度較在矽內增加甚多[34]。 在奈米級的元 件製作時,須特別注意對熱預算(Thermal budget)的監控,以避免造 成NMOS元件嚴重的短通道效應。 (4)自動金屬矽化(Salicide)製程 的熱穩定性。 由於矽鍺的熔點遠較矽為低,因此自動金屬矽化的熱 穩定性易較差,容易會有團聚化(Agglomeration)效應的發生,造成 寄生電阻的增加[35]。 進行相關處理時,亦須嚴加監控。 (5)鍺的

外擴散。在閘氧層熱成長或源/汲植入後的退火等高溫製程時,鍺會有明顯外擴散的情形發生。若表面的應變矽(Strained Si)層太薄,則擴散的Ge成份會造成閘氧層界面態密度(Interface-state Density, Dit)的激增[36],並進一步惡化前述自動金屬矽化熱穩定不佳的現象[37]。要避免此困擾,一般要求應變矽層的厚度須在10奈米以上。(6)自動加熱效應(Self-heating)[38]。由於矽鍺的熱導性遠較矽為差,因此操作時會有類似SOI元件的自動加熱效應情形發生,設計元件與電路時須將此效應考慮在內。

在PMOS中,當使用選擇性磊晶Si<sub>1-x</sub>Ge<sub>x</sub>汲極和源極區域時,縱向單軸壓縮應力(Longitudinal Uniaxial Compressive Stress)施加在通道內,將可增加電洞大約 50 %的移動率。 而在NMOS中,利用一層擴張矽化氮覆蓋層(Tensile Silicon nitride-capping layer),可將擴張應力傳導進NMOSFET以增加電子移動率大約 20 % [30]。 應變矽使用在CMOS元件中,可以分別增加NMOS 10 %及PMOS 25 %的飽和驅動電流。 可見應變技術(Strain Technology)對於先進閘極工程是非常有用的。

「局部機械應力控制」(Local Mechanical-Stress Control, LMC) 為一種新的應變矽製程技術[41],同樣可以有效地用來提高 CMOS 元件的電流驅動能力。 這種機械應力的產生,是使用矽化氮(SiN)層和鍺(Ge)離子的佈值方法來達到選擇性地鬆弛應力。 由選擇性的控制矽化氮層的應力大小,可以改善 n 型通道和 p 型通道 MOSFET的驅動電流。 近年來的研究顯示從矽化氮層而來的機械張力應力會影響驅動電流[38-42],當矽化氮層的機械張力應力增加時,n 型通道的驅動電流增加,但 p 型通道的驅動電流會減少,n 型通道和 p 型通道的驅動電流是與機械應力有相關的。 而局部機械應力控制技術,便可以利用矽化氮的沉積產生機械應力能階以及選擇性的鍺離子佈值,同時達到 NMOS 與 PMOS 元件的驅動電流改善。

造成應變的製程技術非常多,大致上分成單軸應變矽(Uniaxial Strain-Si)技術與雙軸應變矽(Biaxial Strain-Si)技術。例如:藉由覆蓋SiN 當作 Capping Layer 在元件上面、Silicide 造成的應變、STI 製程、SiGe 應用於源極/集極 (Source/Drain)與 Spacer 造成的應變皆可造成單軸的應變。 由於載子在通道內傳導的方向為<110>方向,單軸應變矽技術能在<110>方向造成的 E-K 圖較大的曲率(即較小的有效質量)。 在眾多研究中可發現單軸應變矽技術可有效地使電流驅動力增加。 此外,藉由漸層式 SiGe 在基板上、使用 SOI (Silicon on Insulator)或 SGOI (Silicon Germanium on Insulator)基板等皆為雙軸的應變技術。

#### 1.2 量測方法

#### 1.2.1 漏電流量測

二極體順偏特性可以用方程式(1)表示:

$$Jr = Js (e^{qV/nkT}-1)$$

····· (1)

其中V 是外加偏壓, kT/q=0.026, n 是理想因子。在順向偏壓下,漏電流主要由兩部分組成,分別是從接面空乏區外的擴散電流,和接面空乏區內的復合電流。理想因子的範圍是從1 到2 之間。若是1則表示漏電流主要為擴散電流,若是2 則表示漏電流以產生復合電流為主。

在一個逆向偏壓的接面而言,基本上所有可移動的電子與電洞都被排除於空間電荷區之外。但實際上為了試圖重新建立熱平衡,電子與電洞會經由陷阱能階而產生。也就是說,空乏區中會產生電子與電洞,而且被電場快速移除而產生二極體中另外的電流成分。這種產生過程的示意圖顯示於圖1-1中。產生電流密度(generation current density)可用方程式(2)表示

$$J_{gen} = \frac{en_i W}{2\tau_0} \cdot \cdot \cdot \cdot (2)$$

其中τ<sub>0</sub>為一平均載子生命期,W 為空乏區寬度。因此,逆向偏壓的總電流密度為逆向飽和電流密度與產生電流密度的總和。其電流電壓關係可用方程式(3)表示

$$J_R = J_s + J_{gen} \cdot \cdot \cdot \cdot \cdot (3)$$

逆向飽和電流密度是與逆向偏壓電壓無關的。但Jgen 則是空乏區寬度W 的函數,而W 則是逆向偏壓電壓的函數。因此實際逆向偏壓電與逆向偏壓電壓有關。

接面漏電流與溫度相關的理論已經發展完全。若以逆向漏電流密度在固定逆向偏壓的情形下與溫度作圖,可以得知逆向漏電流密度是由空乏區外的擴散電流或是空乏區內的產生-復合中心所組成。如果逆向漏電流密度主要是由擴散電流為主,則逆向漏電流密度可由方程式(4)表示:

Jr

$$\alpha$$

T<sup>(3+r/2)</sup> exp(-Eg/kT) ····· (4)

其中Eg(eV)是矽的等效能隙,k 是波茲曼常數,T 是絕對溫度, r 是小於1 的值,在這裡忽略不計。如果逆向漏電流密度主要是由 產生電流為主,則逆向漏電流密度可由方程式(5)表示:

Jr α

$$T^{3/2}V^{1/2}$$

exp(-Er/kT) ····· (5)

在這裡V 是指逆向偏壓, Er(eV)是產生-復合中心的能階。在一個理想的二極體,漏電流的產生是由於擴散電流正比於本質載子濃度的平方,在能隙的活化能約為1.1eV。如果二極體的漏電流主要是由於產生-復合電流則活化能約在Eg/2,因為這些能階的等效產生-復合中心靠近矽的半能隙。根據溫度與接面漏電流的理論,逆向偏壓電流主要是由擴散電流與產生電流所組成。

提升鍺P+/N接面二極體漏電流的影響,可以藉由不同面積的二極體之周長與面積的比值(P/A)求得。經由逆向漏電流密度和周長與面積的比值作圖,可得到組成漏電流的二個部分,一個是面積漏電流,另一個是邊緣漏電流,可由方程式(6)表示:

$$Jr = Ja + (P/A)*Jp \cdots (6)$$

其中A(cm<sup>2</sup>)是指二極體的面積,而P(cm)是指二極體的周長,斜率Jp極為周長漏電流密度,直線內插到Y軸(漏電流密度)的數值為面積漏電流密度。

#### 1.2.2 SIMS量測

二次離子質譜儀(SIMS)是將具有足夠能量的一次離子 (primary

ions)撞擊到試樣的表面,經與固體作用後,然後將表面的原子或分子撞擊出來,呈離子狀態的二次離子(secondary ions),收集至質譜儀(mass spectrometer),經質譜之分析,而達到試品表面成份元素之定性及定量分析之研究。另外,由於一次入射離子可以適當的聚焦至徵小點,並且可掃描試片表面,因此方可利用SIMS作顯徵影像分析之觀察。具有高靈敏度的雜質偵測能力,幾乎對所有元素的偵測極限可達百萬分之一原子密度(ppma),對於部份元素的偵測極限甚至可達十億分之一原子密度(ppba)的優越分析能力,而被廣泛的應用於材料分析上,在微電子元件的發展上更扮演了不可或缺的角色

#### 1.3 專題研究動機

近年來很多研究群對於鍺的研究又產生了興趣是因為鍺擁有的電性比矽來的優良,鍺擁有較高的電子電洞遷移率,特別是使用鍺基版的 CMOS 元件時,其低電場的電子遷移率與電洞遷移率是相匹配的;選擇性沉積鍺於自我對準提高源極/汲極(Raised Source/Drain, RSD)的結構能夠有效抑制短通道效應。由於上述的特性,使得鍺在近年來又被進一步的研究。

比較其他金屬矽化物,鍺化鎳(NiGe)在迴火溫度 350℃~500℃的 片電阻與電阻率展現出優良的特性,顯示出鍺化鎳是很有希望成為自 我對準鍺化物於鍺化鎳的接觸技術,並且成為與矽化鎳相當的 CMOS 自我對準金屬矽化物主流製程[43]。

因此在本論文中,我們提出了使用鍺(Ge)以臨場摻雜選擇性磊晶成長(In-situ Doped SEG)的方式製作提高源極/汲極(Raised Source/Drain, RSD)的結構。使用鍺的RSD結構有以下的優點:第一,由於RSD結構能夠解決製作淺接面所面臨的問題;並且在自我對準金屬矽化物(Salicide)製程後,不會破壞淺接面。第二,元件尺寸的縮小使得接面的深度也必須微縮,使得源極/汲極之間的串聯電阻提高;使用RSD結構可以有效改善此問題。第三,由於硼在鍺的固態溶解度比矽來的高,對於接觸電阻而言,高濃度的摻雜於鍺能夠有效

降低鍺與鎳之間的接觸電阻,進一步的降低金屬連線在源極/汲極的接觸電阻。第四,由於提升鍺源極/汲極結構與矽晶格之間的差異可以在元件通道產生應變以提升載子遷移率並且改善元件特性。

#### 1.4 本論文之內容

本研究主要分成三個章節。第一章的內容為介紹本實驗所製作元件的背景,包含提升鍺源極/汲極(Raised Ge Source/Drain)結構的發展、目的以及優點;金屬矽化物(Silicide)製程技術的演進和比較;應變矽(Strain Silicon)製程的簡介以及電性參數與物性量測的方法。

第二章的內容將詳細的描述整個實驗的流程與製程條件。

第三章我們會探討不同堆疊製程條件對提升鍺/矽結構之p<sup>+</sup>/n二極體量測與分析,利用一些參數的改變,來討論其影響電流-電壓曲線的機制及摻雜深度的分析。

第四章是結論與未來方向。

### 第二章

### 元件製程

本實驗將製作不同堆疊結構提升鍺/矽結構p+-n二極體結構作 為探討的主軸,其製程進行在國家奈米實驗室(National Nano Device Laboratories,簡稱NDL)中進行。圖2.1~圖2.5為不同堆疊 結構提升鍺/矽結構p+-n二極體製程流程,以下為詳述此二極體製程 步驟。

#### 2.1 晶片刻號及零層蝕刻

本實驗是採用n-type六吋矽晶片,晶格方向〈100〉,阻值介於 $15~25~\Omega$ -cm之間。首先將所有的晶片以雷射刻號機刻號,方便以後辨識晶片,再用S-tandard C-lean 1-去除刻號時所產生的微粒後,接著開始零層蝕刻的動作,用途是用在以後G-line光學步進機(G-line S-tepper)曝光時晶片位置對準矯正用。

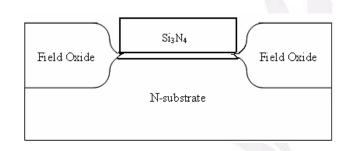

#### 2.2 形成Field Oxide (LOCOS Process)

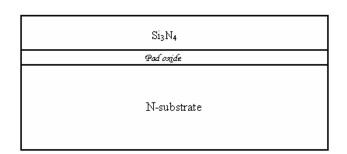

按照標準清洗步驟(Standard Clean)去除晶片表面的雜質,然後

以高溫爐管成長墊氧化層(Pad Oxide)350Å,以及用低壓爐管沈積氮化矽(Si3N4)約1500Å。這兩層的用途分別是:墊氧化層用來抵抗氮化矽(Si3N4)在矽表面所產生的應力,氮化矽則是用來當單幕(Mask)用,藉著其不易被氧滲透的優點來進行場氧化層(Field Oxide)的製作。接著進入微影(Lithography)及乾蝕刻程序,將主動區定義完成,微影時所採用的設備是G-line光學步進機曝光其光波波長為436nm。接著以高溫爐管成長一層約5500Å的場氧化層,以磷酸去除氮化矽後,再以DHF去除墊氧化層,那麼利用LOCOS製成步驟所製作的Field Oxide便已完成,如圖2.1。

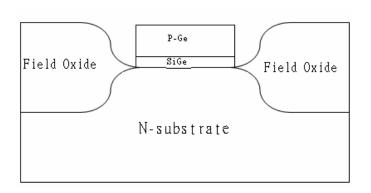

# 2.3 選擇性磊晶成長(Selective Epitaxial Growth)鍺

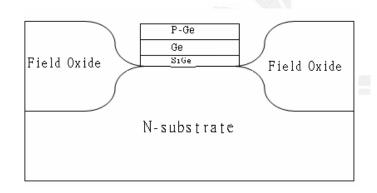

完成標準 LOCOS 製程後,開始選擇性磊晶成長的動作,除了作標準 STD 清洗外,尚須增加 DHF 的清洗步驟來蝕刻晶片表面的自生氧化層,以確實避免因自生氧化層所造成的電性衰減。接著使用超高真空化學氣相沈積系統沈積鍺,使用 UHVCVD 系統沈積的鍺或矽鍺並不會在矽以外的區域沈積,具有自我對準的特性,不需額外使用曝光顯影的製程步驟去除主動區以外的鍺或矽鍺,是非常方便的製程方式。沈積的鍺為矽鍺 100Å/鍺 900Å,以及沉積未掺雜矽鍺 100Å/鍺 300Å,臨

場摻雜 600 Å。

由於矽與鍺的晶格不匹配產生線差排(Threading Dislocation) 會導致元件特性衰退,因此先沈積矽鍺100Å的用途是作為矽與鍺之間 的緩衝層,並且與未沈積矽鍺緩衝層的條件做比較。使用UHVCVD系統 沈積薄膜的過程中以 $B_2$ H<sub>6</sub>作臨場摻雜(In-situ Doping)的氣體,其 流量為40 sccm,如圖2.2。

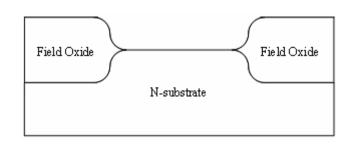

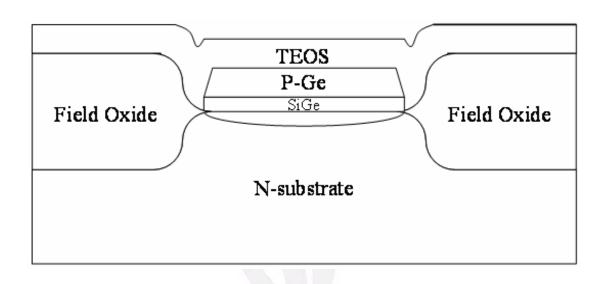

# 2.4 覆蓋保護層(Passivation Layer)與活化(Activation)

在做活化之前,為了避免沈積鍺與非製程氣體產生反應,因此使用電漿輔助化學氣相沈積系統(Plasma Enhanced Chemical Vapor Deposition System, PECVD System),覆蓋一層二氧化矽(SiO2)約1000Å。PECVD系統沈積SiO2所使用的氣體為TEOS(化學式為Si(OC2H5)4)。為了修補因臨場摻雜造成的缺陷,活化是個非常重要的製程步驟。鍺薄膜的活化溫度為850°C,30秒。活化步驟所使用的系統為金屬快速熱退火(Metal Rapid Thermal Annealing System, MRTA)系統,並且在通氮氣(N2)的環境下做活化,如圖2.3。

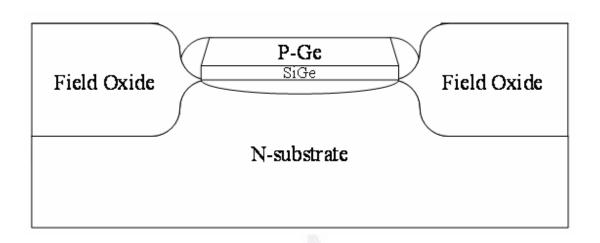

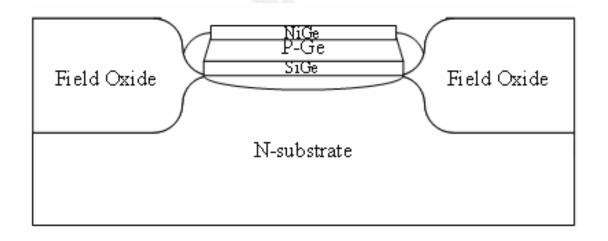

# 2.5 做間隙壁(Spacer)以及金屬矽化物(Silicide)製程

利用先前沈積一層厚度1000Å 的TEOS,在晶片的表面以氧化矽乾式蝕刻機做蝕刻,形成間隙壁,如圖2.4。接著在晶片表面以金屬物理氣相沈積系統鍍上鎳後,以MRTA系統做金屬矽化物製程,製程溫度為400°C,時間為30秒。最後再以經過配製的硫酸去除未反應的鎳,製程即告完成,如圖2.5。

1、n-type 六吋矽晶片,晶格 方向<100> 2、高溫爐管成長墊氧化層 (Pad Oxide) 350Å 3、低壓爐管沉積氮化矽 (Si<sub>3</sub>N<sub>4</sub>) 1500Å

- 4、微影及乾蝕刻,主動區 定義完成

- 5、高温爐長場氧化層 5500

Å

6、磷酸去除氮化矽,DHF去除電氧化層,LOCOS的形成

圖 2.1 LOCOS 的形成

Control Sample 堆疊方式

- 1、STD 清洗

- 2、 DHF 去除自生氧化層

- 3、 UHVCVD 沉積臨場摻

雜矽鍺 100Å/鍺 900Å

Stack Sample 堆疊方式

- 1、STD 清洗

- 2、DHF 去除自生氧化層

- 3、UHVCVD 先沉積未摻雜

矽鍺 100Å/鍺 300Å,

再臨場摻雜 600 Å

圖 2.2 選擇性磊晶矽鍺(SiGe)和鍺(Ge),並以臨場摻雜方式摻雜雜質到鍺層,臨場摻雜的氣體為 $B_2H_6$ ,流量的條件為  $40 \, sccm$ 。

圖 2.3 接著覆蓋一層 TEOS( 即 SiO<sub>2</sub>)作為保護層( Passivation Layer ) ,避免鍺層在活化的步驟中與其他非製程氣體反應活化 ( Activation )製程,除了使鍺層的雜質重新排列,另外使雜質往下擴散,使接面( Junction )在矽鍺與矽的界面之下。

圖 2.4 用乾式蝕刻製作間隙壁(Spacer)

圖 2.5 鍍上鎮(Ni)後作 Silicide 製程,並形成 NiGe。最後用經配製的 硫酸去除未反應的鎮。

# 第三章 不同堆疊結構對提升鍺/矽p<sup>+</sup>-n 二極體特性之影響

#### 3.1 簡介

以RSD結構用來抑制短通道效應與改善元件效能的MOSFETs已經被發展出來。鍺的選擇性磊晶成長能夠有效的製造RSD結構,因為此技術能夠提供臨場摻雜(In-situ doping)。本章節針對提升鍺源極/汲極(Raised Germanium Source/Drain)結構做前期的研究,並用不同堆疊結構作為討論的主軸。我們先製作一個基本的二極體(Diode),也就是接面(Junction)結構。我們將對此p<sup>+</sup>n二極體做一些堆疊的改變,並探討其特性的改變。

参考文獻得知使用UHV-CVD系統沈積鍺薄膜的時間過長,若在沈積薄膜時的氣體流量不穩定會導致薄膜品質不佳,造成量測電流-電壓特性時的良率降低,並且使製程不穩定性提高,所以臨場摻雜所使用的氣體B<sub>2</sub>H<sub>6</sub>,其流量必須達到最大值以確保製程的穩定性。另一方面,由於鍺Silicide製程溫度超過 500℃以上會造成鍺化鎳的結塊,造成鍺化鎳與鍺之間的界面粗糙度增加,使得漏電流增加。

此次實驗便使用不同製程條件所獲得的參數作為最佳條件,並利

用 SIMS 獲得接面深度,探討接面深度對於漏電流的影響。

#### 3.2 量測設計

#### 3.2.1 漏電流

利用Keithley4200,我們隨機量測相同面積、不同結構十五個二極體的I-V特性,電壓從 5V至-3V,面積包含為  $100\mu m^2$ 、 $200\mu m^2$ 、 $300\mu m^2$ 、 $1000\mu m^2$ 。並且觀察每個面積,逆偏於 1V的漏電流分佈。

再經由以上得知數據,逆向漏電流密度和周長與面積的比值作圖,可以得到組成漏電流的兩個部份,一個是面積漏電流,另一個是周長漏電流,可由方程式(1)表示

$$Jr=Ja+(P/A)*Jp-----(1)$$

#### 3.2.2 SIMS 量測

利用二次離子質譜儀(SIMS)量測不同堆疊結構的Sample,選擇面積為  $100\,\mu\,\mathrm{m}^2$ ,來測量元素的成分組成比與深度,分析硼(B)擴散是否擴散到較深的深度,來了解各個結構的接面深度是否有改善,製作出更好的淺接面。

#### 3.3 結果與討論

#### 3.3.1 漏電流分析

此實驗結果選擇面積為  $100\mu m^2$ ,選擇性磊晶的條件分別為Control Sample: 臨場摻雜矽鍺 100Å/鍺 900Å與Stack Sample: 未摻雜的矽鍺 100Å/未摻雜的鍺 300Å/臨場摻雜鍺 600Å,臨場摻雜所使用的氣體  $B_2H_6$ 流量為 40sccm,活化溫度與時間為  $850^{\circ}\text{C}$ ,30 秒,Silicide製程 溫度為  $400^{\circ}\text{C}$ ,30 秒。圖 3.1 比較不同矽鍺/鍺堆疊對二極體I-V電性 之比較,從圖中的順偏(Forward Bias)來看,其 $I_{on}/I_{off}$  current ratio 皆超 過六個級數,再利用式子

$$Jf = Js (e^{qV/nkT}-1)$$

得知理想因子 n (Ideality Factor)分別為 Stack Sample 1.002 與 Control Sample 1.006,表示此二極體的在順偏部份是優良的,表 3.1 是其他面積的理想因子值。

圖 3.2 是逆偏 1V的漏電流分布圖(偉柏圖)。我們隨機量測Control Sample及Stack Sample,已完成且相同面積的十五個二極體,包含面積為 100μm²、200μm²、300μm²、1000μm²。圖 3.2 所顯示的曲線表示本實驗所製作兩種堆疊方示的元件,其均勻性非常的良好,同一面積所量測到的漏電流相差很小。

經由逆偏漏電流密度和周長與面積的比值作圖,可以得到組成漏

電流的兩個部份,一個是面積漏電流,另一個是周長漏電流,可由方程式(1)表示。由圖 3.3 可以得知,即使未經過 Silicide 製程,依然有一定的周長漏電流,Control Sample 的周長漏電流密度為 2.19E-3 A/cm,Stack Sample 的周長漏電流密度為 1.81E-3 A/cm,兩者堆疊方式與傳統 Si 所製作的接面比較,Si 周長漏電流密度為 3.55E-3 A/cm 並無特別明顯的差異。

由於面積越大的二極體所包含的缺陷相對於小面積的二極體的會比較多,因此測量漏電流(單位為A)時所量測到的大面積漏電流會比較大,若把漏電流(A)轉換成漏電流密度(A/cm²) ,則小面積的漏電流密度會比較大,由公式(1)得知,P/A越大表示周長所佔的比例越大,若二極體的周長是逆偏漏電流的主要路徑,則周長漏電流密度(圖 3.3 曲線的斜率)越大。直線內插到Y軸(漏電流密度)的數值即為面積漏電流密度,Control Sample的面積漏電流密度為 2E-8 A/cm²,Stack Sample的面積漏電流密度為 5E-8 A/cm²,兩者堆疊方式與傳統Si所製作的接面比較,Si面積漏電流密度為 2.16E-8 A/cm²相當,可得知此製程不會因為Si、SiGe、Ge晶格長數不同,產生差排缺陷而提高漏電流。

#### 3.3.2 SIMS 分析

由於超高真空化學氣相沈積系統(Ultra High Vacuum Chemical Vapor Deposition System, UHVCVD System) 沈積鍺或矽鍺的速度十

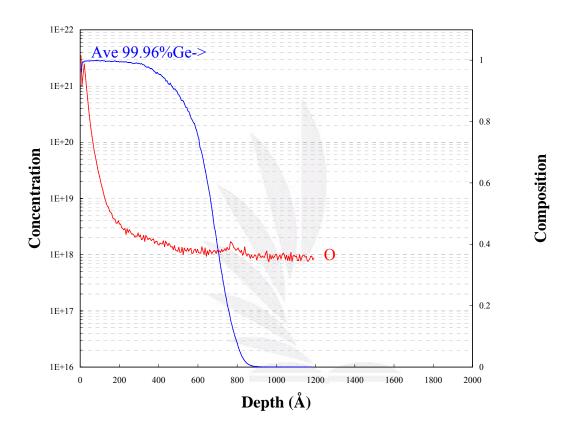

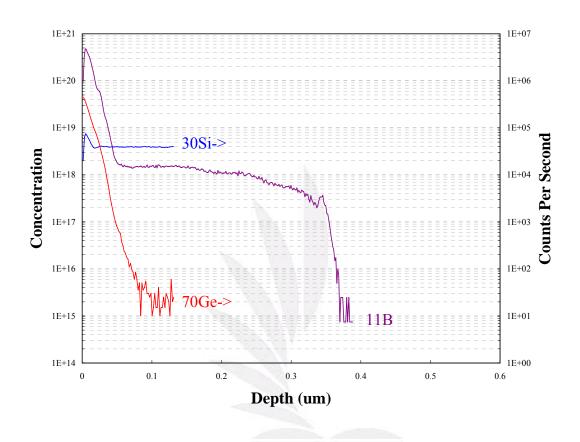

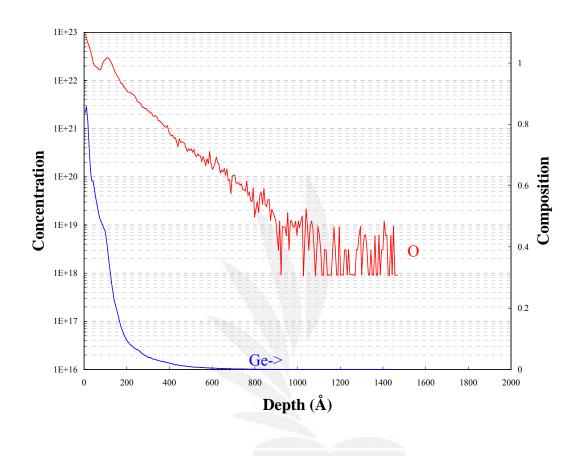

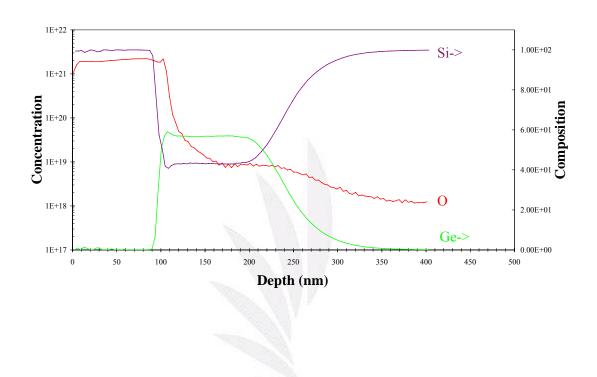

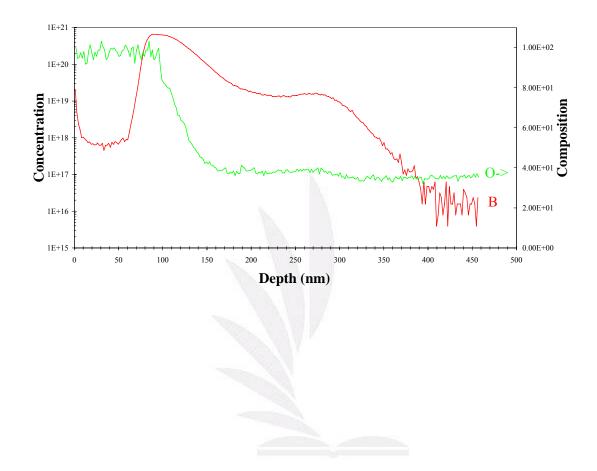

分的緩慢,磊晶成長一片鍺 900Å的時間要 3~4 個小時,若開始沈積 矽鍺和鍺時立即通BoH6作臨場摻雜,經過長時間磊晶後,硼(B)會擴 散到較深的深度,對於超淺接面製程而言是不希望發生的情況。圖 3.4 是在真空環境下做活化的Control Sample的SIMS圖,其中深度 0~700Å的成分為鍺,其雜質濃度在 1E19(cm-3)左右;在鍺與矽的界面 處,雜質濃度更高於 1E20(cm<sup>-3</sup>)。我們所關心的接面深度( Junction Depth )約為 0.3um即 3000Å,表示在一般製程情況下使用臨場摻雜到 鍺層,由於沈積鍺的時間過長,會造成接面深度過深。另一方面,由 於此Sample作活化製程時只有抽真空,並無覆蓋保護層(Passivation Layer),造成表面有輕微的鍺氧化,可由圖 3.5 看出。由於氧化鍺的 結構十分鬆散,被氧化的鍺在高溫的情況下很容易消失不見,因此由 圖 3.4 和圖 3.5 所觀察到的鍺厚度並不如預期般的 900Å。純鍺本身的 熔點為947℃,單純在高溫環境之下並不會揮發不見,若是在高溫含 氧的情況下,會造成鍺的氧化,並使其消失不見。圖 3.6 是在通N<sub>2</sub>O 環境下做活化的Control Simple的SIMS圖,由圖中可看出在深度 0~0.1µm的鍺含量消失十分迅速,圖 3.7 的氧曲線更明顯指出在高溫 的情況下,氧已經擴散到鍺內,造成鍺的氧化並使其消失不見。圖 3.8 是真空環境下做活化的Stack Sample的SIMS圖,除了提供真空環 境做活化,並覆蓋保護層防止因鍺氧化造成製程條件改變,保護層是 使用PECVD系統沈積TEOS,深度在 0~110nm的成分為矽與氧,即二氧化矽。深度在 110nm~230nm的成分是鍺。與圖 3.9 作比較,深度 0~110nm的二氧化矽並無雜質在內,深度 110nm~230nm的硼濃度在 2E19~1E20 左右,此濃度即為鍺內的雜質濃度,以目前製程技術所使用的離子佈植做比較,此雜質濃度只屬於一般摻雜濃度,由於本實驗所使用的摻雜技術為臨場摻雜,並非離子佈植的方式將雜質強制植入,因此摻雜濃度無法達到很高的濃度。深度 230nm~300nm的硼濃度是 2E19 左右,代表接面深度為 700Å左右,與Control Sample的 3000Å相比確實大大地降低硼的擴散。根據圖 3.1、圖 3.4 與圖 3.9 的結果顯示接面深度( Junction Depth )越深,其逆偏漏電流越低,與理論是相符合的。

#### 3.4 結論

在本實驗中,發現超高真空化學氣相沈積系統(Ultra High Vacuum Chemical Vapor Deposition System, UHVCVD System)沈積 鍺,若開始沈積矽鍺和鍺時立即通 $B_2H_6$ 作臨場摻雜,經過長時間磊晶後,硼(B)會擴散到較深的深度。使用Stack Sample結構的二極體有效的降低硼的擴散,但I-V特性並無明顯改變。

圖 3.1 不同堆疊結構之I-V比較,Control代表選擇性磊晶成長In-situ doped SiGe 100Å/In-situ doped Ge 900Å,Stack代表選擇性磊晶成長 Undoped SiGe 100Å/Undoped Ge 300Å/In-situ doped Ge 600Å,其餘製程條件皆相同,並選擇二極體面積 100μm²作比較。

圖 3.2 (a) Stack sample (b) Control sample在-1V的漏電流機率分佈圖 (偉柏圖)。

圖 3.3 Stack sample(空心三角形) and Control sample(空心圓形)在-1V的漏電流密度對周長面積比圖。

圖 3.4 真空環境下做活化的 Control Sample: In-situ doped SiGe 100Å/In-situ doped Ge 900Å 的 SIMS 圖,包含硼(B)的濃度、矽(Si) 和绪(Ge)的成分組成比與深度。

圖 3.5 真空環境下做活化的 Control Sample: In-situ doped SiGe 100Å/In-situ doped Ge 900Å 的 SIMS 圖,包含氧(O)的濃度、鍺(Ge)的成分組成比與深度。

圖 3.6 通  $N_2$ O 環境下做活化的 Control Sample: In-situ doped SiGe 100Å/In-situ doped Ge 900Å的 SIMS圖,包含硼(B)的濃度、矽(Si)和 鍺(Ge)的成分組成比與深度。

圖 3.7 通 $N_2O$ 環境下做活化的Control Sample: In-situ doped SiGe 100Å/In-situ doped Ge 900Å的SIMS圖,包含氧( O )的濃度、鍺( Ge ) 的成分組成比與深度。

圖 3.8 真空環境下做活化的 Stack Sample: Undoped SiGe  $100\text{\AA}/\text{Undoped Ge }300\text{\AA}/\text{In-situ doped Ge }600\text{\AA}$ 的 SIMS 圖,包含氧(O)的濃度、矽(Si)和鍺(Ge)的成分組成比與深度。

圖 3.9 真空環境下做活化的 Stack Sample: Undoped SiGe 100Å/Undoped Ge 300Å/In-situ doped Ge 600Å的 SIMS 圖,包含硼(B)的濃度、氧(O)的成分組成比與深度。

| Sample condition (Sample, contact area) | Ideality factor |

|-----------------------------------------|-----------------|

| Control, 100μm <sup>2</sup>             | 1.006           |

| Control, 200μm <sup>2</sup>             | 1.007           |

| Control, 300μm <sup>2</sup>             | 1.013           |

| Control, 1000μm <sup>2</sup>            | 1.008           |

| Stack, 100µm <sup>2</sup>               | 1.002           |

| Stack, 200µm²                           | 1.005           |

| Stack, 300µm <sup>2</sup>               | 1.009           |

| Stack, 1000μm <sup>2</sup>              | 1.007           |

表 3.1 Control sample 和 Stack sample 的理想因子。

## 第四章 總結

在本實驗中,我們使用矽豬/鍺堆疊結構與一次活化的製程步驟降低漏電流,漏電流受到相當大的改善。當晶格不匹配的兩種材料接觸時並定會產生差排,目前改善鍺與矽差排的製程技術有(1)漸層堆疊法,(2)循環回火法。漸層堆疊法所沈積的薄膜非常厚,製程時間極長,技術複雜,但是薄膜品質非常優異,幾乎無差排的存在。而循環回火法必須做很多次的回火步驟,所使用的熱預算十分龐大,鍺矽介面依然會有差排,但其優點是製程方便。本實驗所使用的方式比上述兩種方式更為簡單,漏電流範圍也控制在一定的等級下。本實驗也提供一種新穎且簡單的製程方式製作淺接面,對未來製作提升鍺源極/汲極提供另一個方向。

在這些製作專題過程中,讓我們對半導體元件有更多的認識與學習並用於實驗測量驗證結果。讓我學到其他的相關知識運用其方法去 獲得參數值最佳化的結果。

感謝指導老師 楊文禄老師的教導與實驗室的學長姊們的指導與 照顧,我將以主動積極、努力認真之學習態度,凡是盡心盡力、全力 參數之萃取精準度,以赴的研究精神來面對任何研究領域,並將專題 中所學,應用於日後的研究上。

## 參考文獻

- [1]J.Nishizawa, K.Aoki and T.Akamine, IEEE Electron Device Letter vol.11, P.105, 1990

- [2]K. Josef Kramer, S. Talwar, A.M. Mccarthy, and K.H. Weiner, "Characterization of Reverse Leakage Components for Ultrashallow p<sup>+</sup>n Diode Fabricated Using Gas Immersion Laser Doping" IEEE Electron Device Lett., vol 17, 1999, pp.461-463.

- [3]Y.Nakahara, K. Takeuchi, T.Tatsumi, Y.Ochiai, S.Mannako, S.Samukawa, and A.Furukawa, "Ultrashallow in situ-doped raised source/drain structure for sub-tenth micro CMOS," in VLSI Tech.Symp.Dig., pp.174-175, 1991

- [4]Shin Nam Hong, Cary A.Ruggles, Jimmie J.Wortman, and Mehmet C.Ozturk "Material and electrical properties of ultrashallow p<sup>+</sup>n junctions formed by low-energy ion implantation and rapid thermal annealing," IEEE Trans. Electron Devices, vol.38, No.3, p476-486, 1991.

- [5]K.Cho, W.R.Allen, T.G.Finstad, W.K.Chu, J.Liu and J.JWortman "Channeling Effect for Low Energy Ion Implantation in Si" Nuclear Instruments and Methods in Physics Research B7/8(1985)265-272.

- [6]Cheng Tung Huang and Tan Fu Lei, "Impact of Ge implantation on the electrical charcteristics of TiSi2 p<sup>+</sup>n shallow junctions with an a-Si buffer" IEEE Trans. Electron Devices, vol.44, no.4, 1997.

- [7]G. A. Ruggles, S. N. Hong, J. J. Wortman, M. Ozturk, D. R. Myers, J. J. Hren, and R. B. Fair," A comparison of low energy BF<sub>2</sub> implatation in Si and Ge preamorphized silicon" In Mat. Res. Soc. Symc. Pros., vol.128, pp.611-616, 1989

- [8]C.M. Osburn, D. F. Downey, S. B. Felch and B. S. Lee, Ion Implantation Technology-96, IEEE Press, 1997, p.697.

- [9]Y.Nakahar;s, KTakeuchi, T.Tatsumi, Y.Ochiai\*, S.Manako\*, S.Samukawa and A.Furukawa,"Ultra-shallow in-situ-doped raised sourceldrain structure for sub-tenth micron CMOS" IEEE VLSI, 1996

- [10]A. Waite. A.G.R. Evans and N. Afshar-Hanaii,"Electrical stressing of submicrometre MOSFETs with raised source/drain structures realized by selective epitaxial growth of silicon using silane only." IEEE electronics letters Vol. 30 No. 17 1994.

- [11]Q.F. Wang, C.M. Osburn, and C.A.Canovai, "Ultrashallow junction formation using Silicide as Diffusion source and low thermal budget,"

- IEEE Trans. Electron Devices, vol.39, p.2486, 1992

- [12]D. L. kwong, T. H. Ku., S. K. Lee, E. Louis, N. S. Alvi, and P. Chu, "Silicided shallow junction formation by ion implantation of impurity ions into silicide layers and subsequent drive-in," J.Appl. Phys., vol.61, p.5084, 1987

- [13]S.B. Herner, H. J. Gossmann, R. T. Tung, and B. P. Gila, "Ultrashallow junction in silicon using single-crystal CoSi<sub>2</sub> as a dopant source" J. Electrochemical and Solid-State letters. Vol.1, p.150-152, 1998

- [14] I. Polishchuk, P. Ranade, T.-J. King, and C. Hu, "Dual work function metal gate CMOS transistors by Ni-Ti interdiffusion," IEEE Electron Device Lett., vol. 23, pp. 200–202, Apr. 2002

- [15] K. Maex, Material Science and Engineering, R11, (1993)

- [16] 莊達人, "VLSI 製造技術," 高立圖書, 1994

- [17] J. P. Lu, D. Miles, J. Zhao, A. Gurba, Y. Xu, C. Lin, M. Hewson, J. Ruan, L. Tsung, R. Kuan, T. Grider, D. Mercer, and C. Montgomery, "A novel nickel SALICIDE process technology for CMOS devices with sub-40 nm physical gate length," in IEDM Tech. Dig., 2002, pp. 371–374.

- [18] L. R. Zheng, L. S. Hung, and J.W. Mayer, "Redistribution of dopant arsenic during silicide formation," J. Appl. Phys., vol. 58, pp. 1505–1514, 1985.

- [19] S. M. Sze, Semiconductor Devices Physics and Technology, AT & T Bell Lab, Inc. 1985

- [20] J. R. Brews, et al., IEEE Electron Devices Lett., EDL-1, 2, 1980.

- [21] T. Moromoto, T. Ohguro, H. S. Momose, ect, T. Iinuma, I. Kunishima, K. Shguro. Ect., "Self-Aligned Nickel-Mono-Silicide Technology for High-Speed Deep Submicrometer Logic CMOS ULSI," IEEE Trans. Electron Devices. vol. 42, no. 5, p. 915-923, 1995

- [22] J. B. Lasky, J. S. Nakos, O. J. Cain, P. J. Geiss, "Comparison of transformation to low-resistivity phase and agglomeration of TiSi<sub>2</sub> and CoSi<sub>2</sub>," IEEE Tran. Electron Devices, ED-38, p. 262 (1991)

- [23] T. Ohguro, S. Nakamura, M. Koike, T. Morimoto, A. Nishiyama, Y. Ushiku, etc. "Analysis of Resistance Behavior in Ti- and Ni-salicide Polysilicon Films," IEEE Trans. Electron Devices. vol. 41 no. 12, p. 2305-2316, 1994

- [24] H. Iwai, T. Ohguro, S. I. Ohmi, "NiSi salicide technology for scaled CMOS," Microelectronic Engineering 60 (2002) 157–169

- [25] F. Deng, R. A. Johnson, P. M. Asbeck, S. S. Lau, W. B. Dubbelday, T. Hsiao, and J. Woo, "Salicidation process using NiSi and its device application," J. Appl. Phys. 81, 8047 (1997)

- [26] T. Morimoto, T. Ohguro, S. Momose, T. Iinuma, I. Kunishima, K. Suguro, I. Katakabe, H. Nakajima, M. Tsuchiaki, M. Ono, Y. Katsumata, H. Iwai, "Self-aligned nickel-mono-silicide technology for high-speed deep submicrometer logic CMOS ULSI," IEEE Tran. Electron Devices, ED-42, p. 915 (1995)

- [27] K. Inoue, K. Mikagi, H. Abiko, T. Kikkawa, "A new cobalt salicide technology for 0.15 μm CMOS using high-temperature sputtering and in-situ vacuum annealing," Proc. IEDM, p. 445 (1995).

- [28] K. Goto, I. Fushida, J. Watanabe, T. Sukegawa, K. Kawamura, T. Yamazaki, T. Sugii, "Leakage mechanism and optimized conditions of Co salicide process for deep-submicron CMOS devices," Proc. IEDM, p. 449 (1995).

- [29] Q. Z. Hong et al., "CoSi<sub>2</sub> with low diode leakage and low sheet resistance at 0.065 μm gate length," Proc. IEDM, p.107 (1997).

- [30] Scott E. Thompson, Mark Armstrong, Chis Auth, Mohsen Alavi, Mark Buehler, Robert Chau, Steve Cea, Tahir Ghani, Glenn Glass, Thomas Hoffman, Chia-Hong Jan, Chis Kenyon, Jason Klaus, Kelly Kuhn, Zhiyong Ma, Brian Mcintyre, Kaizad Mistry, Anand Murthy, Borna Obradovic, Ramune Nagisetty, Phi Nguyen, Sam Sivakumar, Reaz Shaheed, Lucian Shifren, Bruce Tufts, Sunit Tyagi, Mark Bohr, and Youssef El-Mansy, "A 90-nm Logic Technology Featuring Strained-Silicon," IEEE TRANSACTIONS ON ELECTRON DEVICES, pp.1790-1797, VOL. 51, NO. 11, NOVEMBER 2004

- [31] Hoyt, J.L. Nayfeh, H.M. Eguchi, S. Aberg, I. Xia, G. Drake, T. Fitzgerald, E.A.Antoniadis, D. A., "Strained silicon MOSFET technology," Tech. Dig. IEDM, pp. 23-26, 2002

- [32] Thompson, S. Anand, N. Armstrong, M. Auth, C, Arcot, B. Alavi, M. Bai, P. Bielefeld, J. Bigwood, R. Brandenburg, J. Buehler, M. Cea, S. Chikarmane, V. Choi, C. Frankovic, R. Ghani, T. Glass, G. Han, W. Hoffmann, T. Hussein, M. Jacob, P. Jain, A. Jan, C. Joshi, S. Kenyon, C. Klaus, J. Klopcic, S. Luce, J. Ma, Z. Mcintyre, B. Mistry, K. Murthy, A. Nguyen, P. Pearson, H. Sandford, T. Schweinfurth, R. Shaheed, R. Sivakumar, S. Taylor, M. Tufts, B. Wallace, C. Wang, P.

- Weber, C. Bohr, M. "A 90 nm logic technology featuring 50 nm strained silicon channel transistors, 7 layers of Cu interconnects, low k ILD, and 1 /spl mu/m/sup 2/ SRAM cell," Tech. Dig.IEDM, pp. 61-64, 2002

- [33] Sugii, N. Hisamoto, D. Washio, K. Yokoyama, N. Kimura, S., "Enhanced performance of strained Strained-Si MOSFETs on CMP sige virtual substrate," Tech. Dig. IEDM, pp. 737-740, 2001

- [34] Rim, K. Chu, J. Chen, H. Jenkins, K.A. Kanarsky, T. Lee, K. Mocuta, A. Zhu, H. Roy, R. Newbury, J. Ott, J. Petrarca, K. Mooney, P. Lacey, D. Koester, S.Chan, K.Boyd, D. Ieong, M. Wong, H.-S., "Characteristics and device design of sub-100 nm strained Si N- and PMOSFETs," Symp. VLSI Technol, pp.98-99, 2002

- [35] Mizuno, T. Sugiyama, N. Tezuka, T. Numata, T. Maeda, T. Takagi, S., "Design for scaled thin film strained-SOI CMOS devices with higher carrier mobility," Tech. Dig. IEDM, pp. 31-34, 2002

- [36] Lee, B.H. Mocuta, A. Bedell, S. Chen, H. Sadana, D, Rim, K. O'Neil, P. Mo, R. Chan, K. Cabral, C. Lavoie, C. Mocuta, D. Chakravarti, A. Mitchell, P. Haensch, W. Welser, J., "Performance enhancement on sub-70 nm strained silicon SOI MOSFETs on ultra-thin thermally mixed strained silicon/SiGe on insulator (TM-SGOI) substrate with raised S/D," Tech. Dig. IEDM, pp. 946-948, 2002

- [37] Rim, K. Hoyt, J.L. Gibbons, J.F. "Transconductance enhancement in deep submicron strained Si n-MOSFETs," Tech. Dig. IEDM, pp. 707-710, 1998

- [38] A. Shimizu, K. Hachimine, N. Ohki, H. Ohta, M. Koguchi, Y. Nonaka, H. Sato, and F. Ootsuka, "Local Mechanical-Stress Control (LMC): A New Technique for CMOS-Performance Enhancement," IEDM Tech. Dig.,pp. 433-436. .2001.

- [39] J. Welser, J.L. Hoyt, S. Takagi, and J.F. Gibbons, "Strain dependence of the performance enhancement in strained-Sin-MOSFETs" IEDM Tech. Dig.,pp. 373-376. 1994.

- [40] K. Rim, S.Koester, M.Hargrove, J.Chu, P.M. Mooney, J. Ott, T. Kanarsky, P.Ronsheim, M.Ieong, A.Grill and H.P. Wong, "Strained Si NMOSFETs for high performance CMOS technology" on VLSI Tech.,pp 59-60. 2001

- [41] F. Ootsuka, S. Wakahara, K. Ichinose, A. Honzawa, S. Wada, H. Sato, T. Ando, H. Ohta, K. Watanabe, and T. Onai "A Highly Dense, High-Performance 130nm node CMOS Technology for Large Scale

- System-on-a -Chip Applications" IEDM Tech. Dig.,pp. 575-578. 2000.

- [42] S. Ito, H. Namba, K. Yamaguchi, T. Hirata, K. Ando, S. Koyama, S. Kuroki, N. Ikezawa, T. Suzuki, T. Saitoh, and T. Horiuchi "Mechanical Stress Effect of Etch-Stop Nitride and its Impact on Deep Submicron Transistor Design" IEDM Tech. Dig.,pp. 247-250. 2000

- [43] Shih-Lu Hsu, Chao-Hsin Chien,a! Ming-Jui Yang, Rui-Hao Huang, Ching-Chich Leu, and Shih-Wen Shen." Study of thermal stability of nickel monogermanide on single- and polycrystalline germanium substrates" APPLIED PHYSICS LETTERS 86 2005.